# Lecture Notes in Computer Science

4419

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich. Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Pedro C. Diniz Eduardo Marques Koen Bertels Marcio Merino Fernandes João M.P. Cardoso (Eds.)

# Reconfigurable Computing: Architectures, Tools and Applications

Third International Workshop, ARC 2007 Mangaratiba, Brazil, March 27-29, 2007 Proceedings

#### Volume Editors

Pedro C. Diniz

Instituto Superior Técnico (IST)/INESC-ID Departamento de Engenharia Informática (DEI) Tagus Park, 2780-990 Porto Salvo, Portugal

E-mail: pedro.diniz@tagus.istl.utl.pt

Eduardo Marques

Universidade de São Paulo

Instituto de Ciências Matemáticas e de Computação (ICMC)

P.O. Box 668, 13560-970 São Carlos, Brazil

E-mail: emarques@icmc.usp.br

Koen Bertels

Delft University of Technology

Computer Engineering Lab

Mekelweg 4, 2628 CD Delft, The Netherlands

E-mail: k.l.m.bertels@ewi.tudelft.nl

Marcio Merino Fernandes

Universidade Metodista de Priacicaba

Programa de Mestrado em Ciência da Computação Campus Taquaral

13400-911 Piracicaba-SP, Brazil E-mail: mmfernan@unimep.br

João M.P. Cardoso

INESC-ID, Instituto Superior Técnico (IST)

Av. Alves Redol 9, 1000-029, Lisbon, Portugal

E-mail: jmpc@acm.org

Library of Congress Control Number: 2007922940

CR Subject Classification (1998): C, B, I.4

LNCS Sublibrary: SL 1 – Theoretical Computer Science and General Issues

ISSN 0302-9743

ISBN-10 3-540-71430-8 Springer Berlin Heidelberg New York ISBN-13 978-3-540-71430-9 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2007

Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12035847 06/3142 5 4 3 2 1 0

#### Preface

Reconfigurable computing platforms have been gaining wide acceptance, spanning a wide spectrum from highly specialized custom controllers to general-purpose high-end computing systems. They offer the promise of increasing performance gains by exploiting coarse-grain as well as fine-grain instruction level parallelism opportunities given their ability to implement custom functional, storage and interconnect structures. With the continuous increase in technology integration, leading to devices with millions of logic gates, ready to be programmed according to the (run-time) application needs, it is now possible to implement very sophisticated and reconfigurable systems. Configurability is seen as a key technology for substantial product life-cycle savings in the presence of evolving product requirements and/or interfaces or standards. The extreme configurability and flexibility also makes reconfigurable architectures the medium of choice for very rapid system prototyping or early design verification.

The relentless capacity growth of reconfigurable devices, such as FPGAs (Field-Programmable Gate Arrays), is creating a wealth of new opportunities and increasingly complex challenges. Recent generation devices have heterogeneous internal resources such as hardware multiplier units and memory blocks in addition to a vast amount of fine grain logic cells. Taking advantage of the wealth of resources in today's configurable devices is a very challenging problem. Although the inclusion of FPGAs in mainstream computing products clearly shows that this technology is maturing, many aspects still require substantial research to effectively deliver the promise of this emerging technology.

A major motivation for the International Applied Reconfigurable Computing  $(ARC)^1$  workshop series is to provide a forum for presentation and discussion of on-going research efforts, as well as more elaborated, interesting and high-quality work, on applied reconfigurable computing. The workshop also focuses on compiler and mapping techniques, and new reconfigurable computing architectures.

The ARC series started in 2005 in the Algarve, Portugal. The second workshop (ARC 2006) took place in Delft, The Netherlands in March 2006, and the selected papers were published as a Springer LNCS (Lecture Notes in Computer Science) volume<sup>2</sup>. The success of previous workshops clearly reveals the growing interest of academia and industry and thus the timeliness of this forum.

This LNCS volume includes the papers selected for the third workshop (ARC 2007), held at Mangaratiba, Rio de Janeiro, Brazil, on March 27–29, 2007. The workshop attracted a large number of very good papers, describing interesting work on reconfigurable computing related subjects. A total of 72 papers

<sup>&</sup>lt;sup>1</sup> http://www.arc-workshop.org

<sup>&</sup>lt;sup>2</sup> Koen Bertels, João M. P. Cardoso, and Stamatis Vassiliadis (Eds.), Reconfigurable Computing: Architectures and Applications, Second International Workshop, ARC 2006, Delft, The Netherlands, March 2006, Revised Selected Papers, Springer Lecture Notes in Computer Science, LNCS 3985, August 2006.

were submitted to the workshop from 20 countries: The Netherlands (4), France (3), Germany (4), Republic of South Korea (12), Brazil (14), People's Republic of China (8), Denmark (1), Mexico (2), Portugal (2), South Africa (1), Lebanon (1), Australia (1), Republic of Ireland (2), Puerto Rico (1), Spain (5), UK (2), India (2), Japan (5), Poland (1), and Greece (1). Submitted papers were evaluated by at least three members of the Program Committee. After careful selection, 27 papers were accepted for presentation as full papers (37.5% of the total number of submitted papers) and 10 as short papers (global acceptance rate of 51.4%). This volume also includes an article from the 2006 ARC workshop, which was, by lapse, not included in the 2006 proceedings. Those accepted papers led to a very interesting workshop program, which we considered to constitute a representative overview of ongoing research efforts in reconfigurable computing, a rapidly evolving and maturing field.

Several persons contributed to the success of the workshop. We would like to acknowledge the support of all the members of this year's workshop Steering and Program Committees in reviewing papers, in helping with the paper selection, and in giving valuable suggestions. Special thanks also to the additional researchers who contributed to the reviewing process, to all the authors who submitted papers to the workshop, and to all the workshop attendees. We also acknowledge the generous financial contribution from Altera Corp., USA and PI Componentes, Brazil. Last but not least, we are especially indebted to our colleague Jürgen Becker from the University of Karlsruhe for his strong support of this workshop.

We are grateful to Springer, particularly Mr. Alfred Hofmann and the LNCS Editorial, for their support and work in publishing this book.

January 2007

Pedro C. Diniz Eduardo Marques Koen Bertels Marcio M. Fernandes João M. P. Cardoso

# Organization

The 2007 Applied Reconfigurable Computing workshop (ARC 2007) was organized by the Institute of Mathematics and Computer Science (ICMC) of the University of São Paulo (USP) in São Carlos, Brazil.

# Organization Committee

General Chairs Eduardo Marques (ICMC-USP, Brazil)

Koen Bertels (Delft University of Technology,

The Netherlands)

Program Chair Pedro C. Diniz (IST/INESC-ID, Portugal)

Proceedings Chair Marcio Merino Fernandes (UNIMEP, Brazil)

Finance Chair Jorge Luiz e Silva, ICMC-USP, Brazil Sponsorship Chair Denis F. Wolf, ICMC-USP, Brazil

Web Chair

Carlos R. P. Almeida Jr. (ICMC-USP, Brazil)

Special Journal Edition Chair

George Constantinides (Imperial College, UK)

Loão M. P. Cardoso (IST/INESC ID, Portugal)

João M. P. Cardoso (IST/INESC-ID, Portugal)

Local Arrangements Chairs Marcos J. Santana, ICMC-USP, Brazil

Regina H. C. Santana, ICMC-USP, Brazil

Leisure Chairs Ricardo Menotti, UTFPR, Brazil

Vanderlei Bonato, ICMC-USP, Brazil

Publicity Chair Fernanda Lima Kastensmidt, UFRGS, Brazil

# Steering Committee

George Constantinides, Imperial College, UK

João M. P. Cardoso, IST/INESC-ID, Portugal

Koen Bertels, Delft University of Technology, The Netherlands

Mladen Berekovic, IMEC vzw, Belgium Pedro C. Diniz, IST/INESC-ID, Portugal

Stamatis Vassiliadis, Delft University of Technology, The Netherlands

Walid Najjar, University of California Riverside, USA

# Program Committee

Andreas Koch, Technical University of Darmstadt (TU), Germany Andy Pimentel, University of Amsterdam, The Netherlands

#### VIII Organization

António Ferrari, University of Aveiro, Portugal

Bernard Poitier, University of West Brittany (UBO), France

Carl Ebeling, University of Washington, USA

Eduardo Marques, University of São Paulo, Brazil

George Constantinides, Imperial College, UK

Hideharu Amano, Keio University, Japan

Horácio Neto, IST/INESC-ID, Portugal

Jeff Arnold, Strech Inc., USA

Joachim Pistorius, Altera Corp., USA

João M. P. Cardoso, IST/INESC-ID, Portugal

Joon-seok Park, Inha University, Inchon, Republic of South Korea

José Nelson Amaral, University of Alberta, Canada

José Sousa, IST/INESC-ID, Portugal

Juan Carlos de Martin, Politecnico di Torino, Italy

Jürgen Becker, University of Karlsruhe (TH), Germany

Koen Bertels, Delft University of Technology, The Netherlands

Laura Pozzi, University of Lugano (USI), Switzerland

Marco Platzner, University of Paderborn, Germany

Maria-Cristina Marinescu, IBM T. J. Watson Research Center, USA

Markus Weinhardt, PACT XPP Technologies AG, Germany

Mihai Budiu, Microsoft Research, USA

Mladen Berekovic, IMEC vzw, Belgium

Nader Bagherzadeh, University of California Irvine, USA

Oliver Diessel, University of New South Wales, Australia

Paul Chow, University of Toronto, Canada

Pedro C. Diniz, IST/INESC-ID, Portugal

Pedro Trancoso, University of Cyprus, Cyprus

Peter Cheung, Imperial College, UK

Phil James-Roxby, Xilinx Corp., USA

Philip Leong, The Chinese University of Hong Kong,

People's Republic of China

Ranga Vemuri, University of Cincinnati, USA

Reiner Hartenstein, University of Kaiserslautern, Germany

Roger Woods, The Queen's University of Belfast, UK

Roman Hermida, Universidad Complutense, Spain

Russell Tessier, University of Massachusetts, USA

Ryan Kastner, University of California Santa Barbara, USA

Seda Ö. Memik, Northwestern University, USA

Stamatis Vassiliadis, Delft University of Technology, The Netherlands

Stephan Wong, Delft University of Technology, The Netherlands

Tarek El-Ghazawi, The George Washington University, USA

Tim Callahan, Carnegie Mellon University, USA

Tsutomu Sasao, Kyushu Institute of Technology, Japan

Walid Najjar, University of California Riverside, USA

Wayne Luk, Imperial College, UK

#### Additional Reviewers

Akira Hatanaka, University of California Irvine, USA

Alastair Smith, Imperial College, UK

António Roldão Lopes, Imperial College, UK

Betul Buyukkurt, University of California Riverside, USA

Bhishek Mitra, University of California Riverside, USA

Denis F. Wolf, ICMC/USP, Brazil

Esam El-Araby, The George Washington University, USA

Eoin Malins, The Queen's University of Belfast, UK

Florian-Wolfgang Stock, PACT XPP Technologies AG, Germany

Holger Lange, Technical University of Darmstadt, Germany

Ivan Gonzalez, The George Washington University, USA

Jason Villareal, University of California Riverside, USA

João Bispo, INESC-ID, Portugal

John McAllister, The Queen's University of Belfast, UK

Jonathan Clarke, Imperial College, UK

Jorge Luiz e Silva, ICMC/USP, Brazil

José Arnaldo de Holanda, ICMC/USP, Brazil

Jun Ho Bahn, University of California Irvine, USA

Kazuaki Tanaka, Kyushu Institute of Technology, Japan

Kieron Turkington, Imperial College, UK

Lih Wen Koh, University of New South Wales Asia, Singapore

Marcio Merino Fernandes, UNIMEP, Brazil

Mário Véstias, ISEL/INESC-ID, Portugal

Mohamed Taher, The George Washington University, USA

Nikolaos Vassiliadis, Aristotle University of Thessaloniki, Greece

Rafael Peron, ICMC/USP, Brazil

Ricardo Menotti, ICMC/USP, Brazil

Scott Fischaber, The Queen's University of Belfast, UK

Shannon Koh, University of New South Wales Asia, Singapore

Shinobu Nagayama, Kyushu Institute of Technology, Japan

Su-Shin Ang, Imperial College, UK

Syed Murtaza, University of Amsterdam, The Netherlands

Vanderlei Bonato, ICMC/USP, Brazil

Yasunori Osana, Keiko University, Japan

Yukihiro Iguchi, Kyushu Institute of Technology, Japan

Zhi Guo, University of California Riverside, USA

# Sponsoring Institutions

USP - Universidade de São Paulo

CAPES - Coordenação de Aperfeiçoamento de Pessoal de Nível Superior

# **Table of Contents**

| Architectures [Regular Papers]                                                                                                      |   |

|-------------------------------------------------------------------------------------------------------------------------------------|---|

| Frank Bouwens, Mladen Berekovic, Andreas Kanstein, and                                                                              | 1 |

| Georgi Gaydadjiev                                                                                                                   |   |

| A Configurable Multi-ported Register File Architecture for Soft Processor Cores                                                     | 4 |

| MT-ADRES: Multithreading on Coarse-Grained Reconfigurable                                                                           |   |

| Architecture                                                                                                                        | 6 |

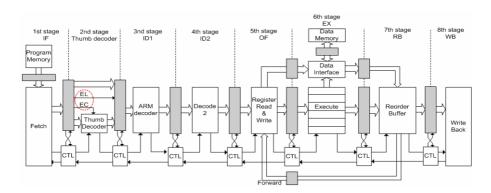

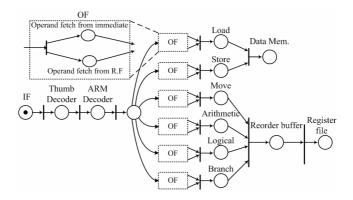

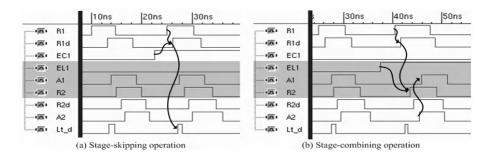

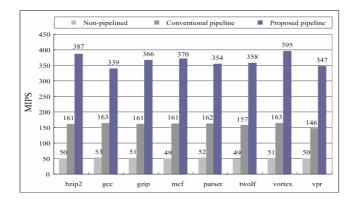

| Asynchronous ARM Processor Employing an Adaptive Pipeline                                                                           |   |

| Architecture                                                                                                                        | 9 |

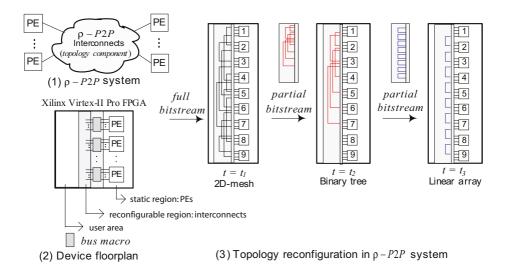

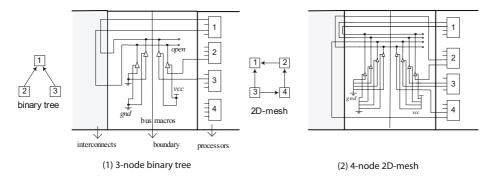

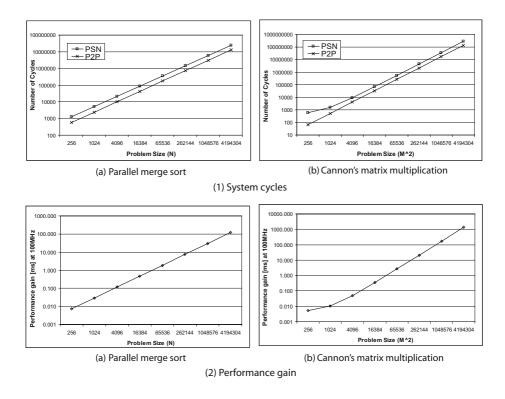

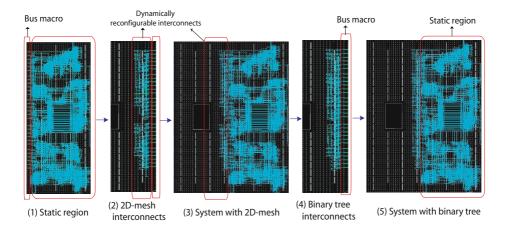

| Partially Reconfigurable Point-to-Point Interconnects in Virtex-II Pro                                                              |   |

| FPGAs                                                                                                                               | 9 |

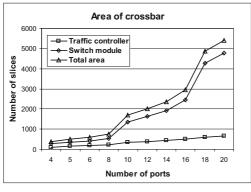

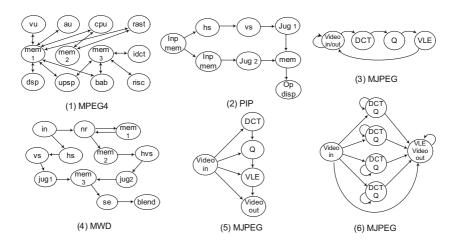

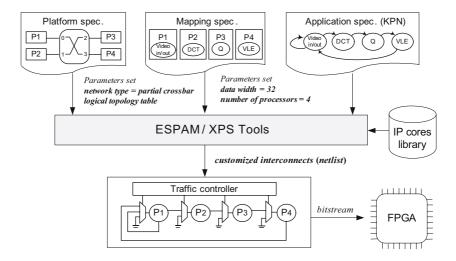

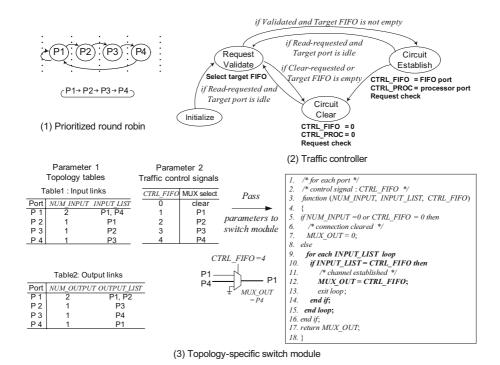

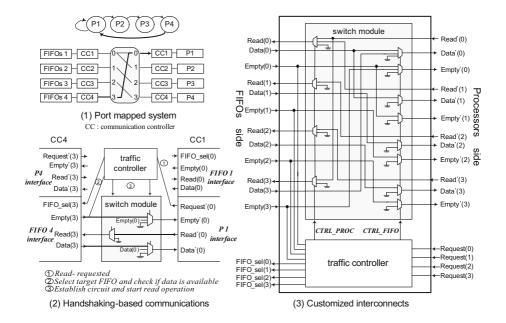

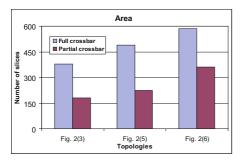

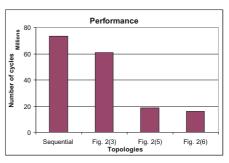

| Systematic Customization of On-Chip Crossbar Interconnects 6  Jae Young Hur, Todor Stefanov, Stephan Wong, and Stamatis Vassiliadis | 1 |

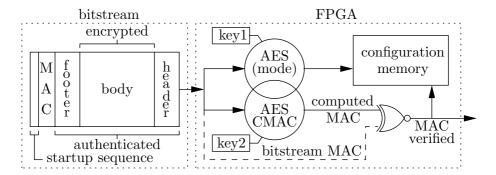

| Authentication of FPGA Bitstreams: Why and How                                                                                      | 3 |

| Architectures [Short Papers]                                                                                                        |   |

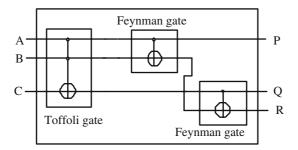

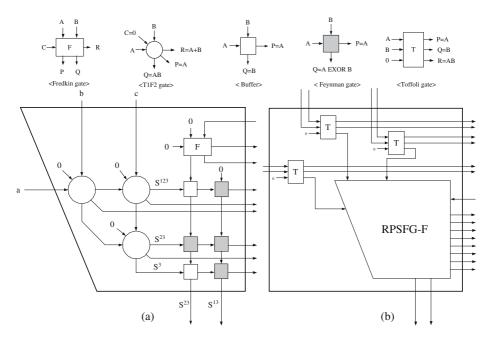

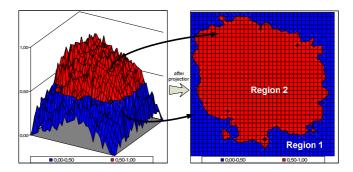

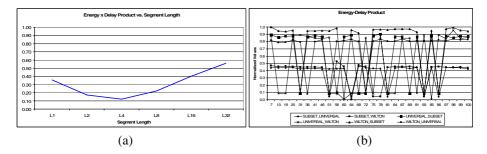

| Design of a Reversible PLD Architecture                                                                                             | 5 |

| Designing Heterogeneous FPGAs with Multiple SBs                                                                                     | 1 |

| Mapping Techniques and Tools [Regular Papers]                                                                                       |   |

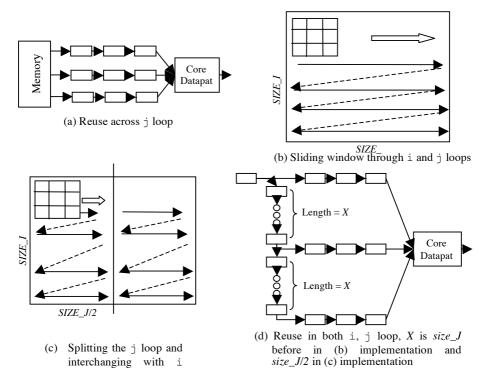

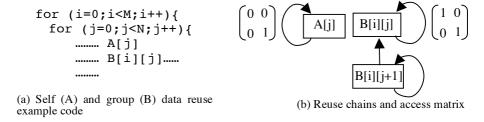

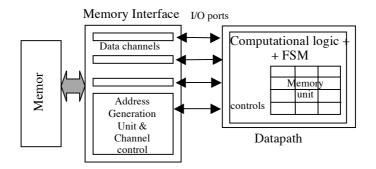

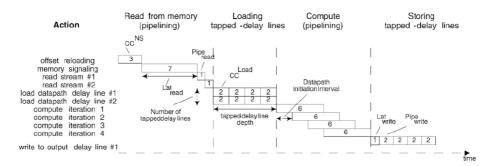

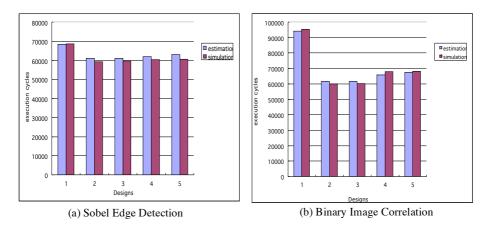

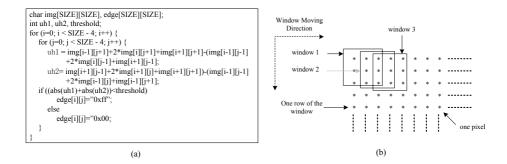

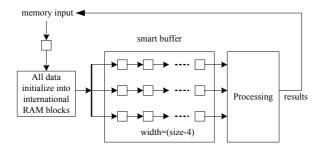

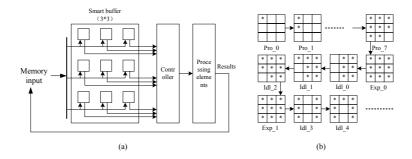

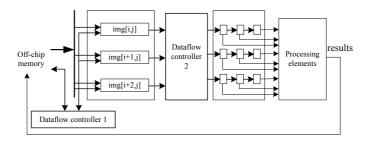

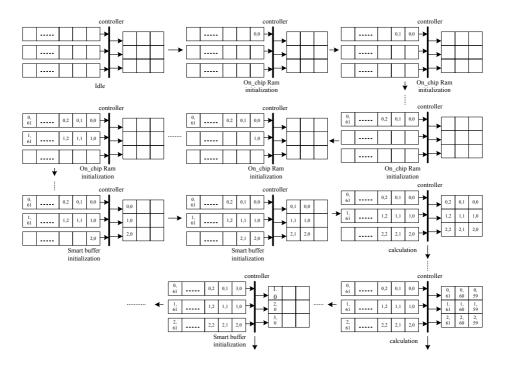

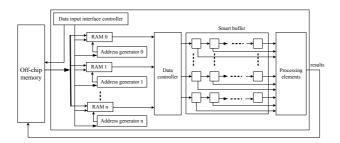

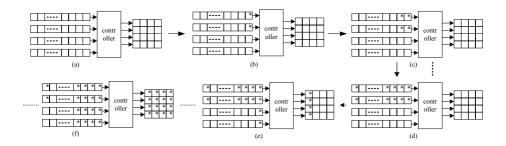

| Partial Data Reuse for Windowing Computations: Performance Modeling for FPGA Implementations                                        | 7 |

| Operations onto Reconfigurable Hardware                                                                             | 110 |

|---------------------------------------------------------------------------------------------------------------------|-----|

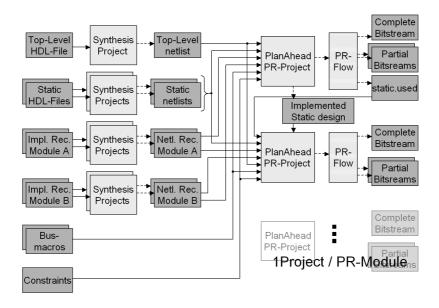

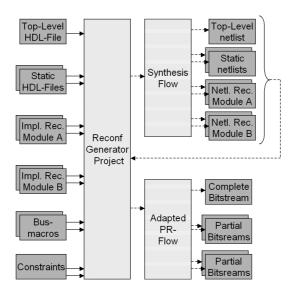

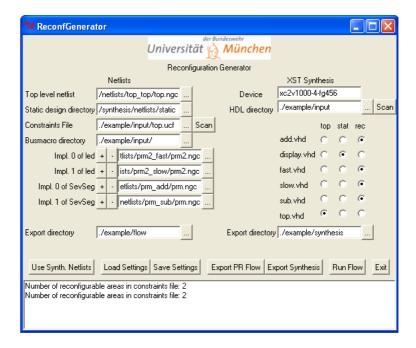

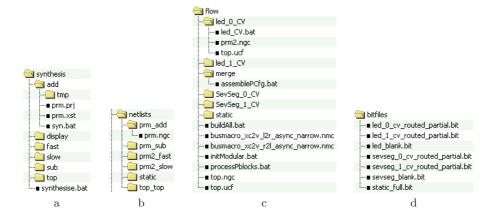

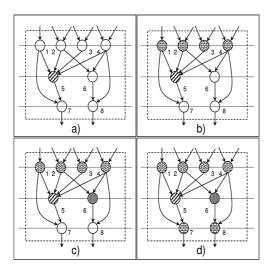

| Adapting and Automating XILINX's Partial Reconfiguration Flow for Multiple Module Implementations                   | 122 |

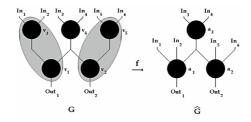

| A Linear Complexity Algorithm for the Automatic Generation of<br>Convex Multiple Input Multiple Output Instructions | 130 |

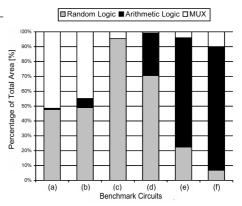

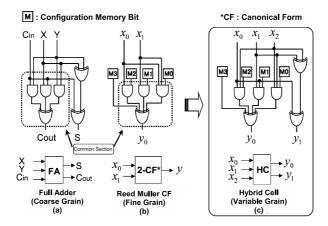

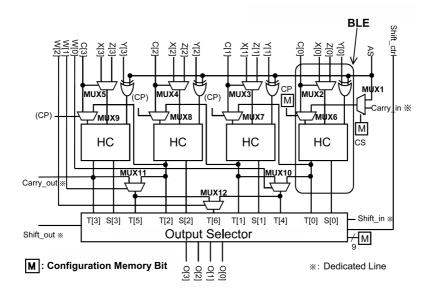

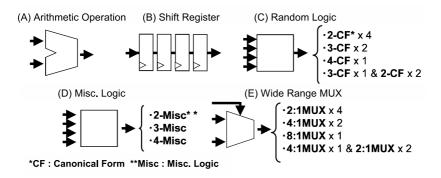

| Evaluating Variable-Grain Logic Cells Using Heterogeneous Technology Mapping                                        | 142 |

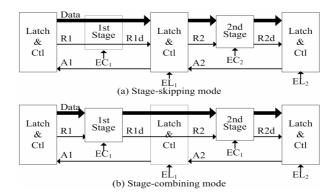

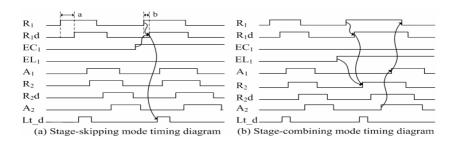

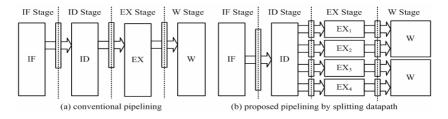

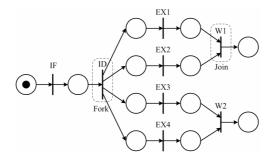

| The Implementation of a Coarse-Grained Reconfigurable Architecture with Loop Self-pipelining                        | 155 |

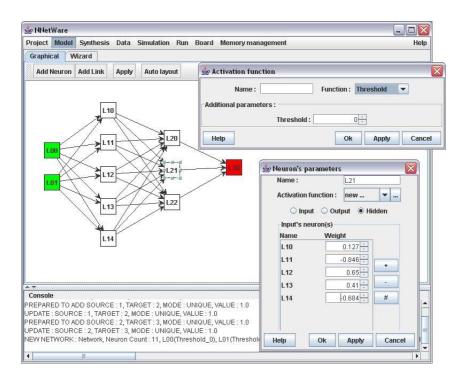

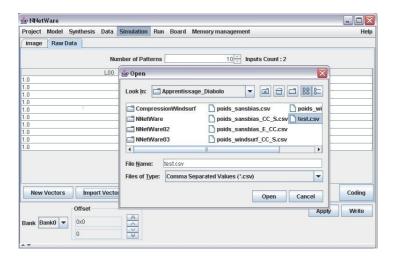

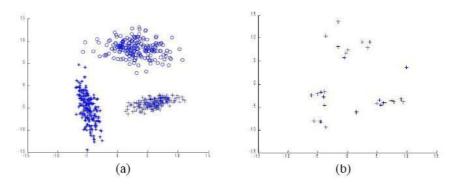

| Hardware/Software Codesign for Embedded Implementation of Neural Networks                                           | 167 |

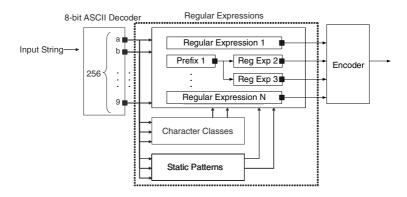

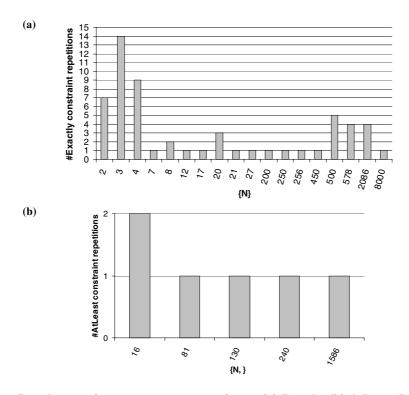

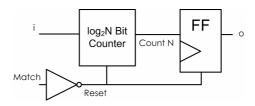

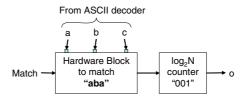

| Synthesis of Regular Expressions Targeting FPGAs: Current Status and Open Issues                                    | 179 |

| Mapping Techniques and Tools [Short Papers]                                                                         |     |

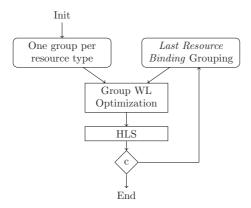

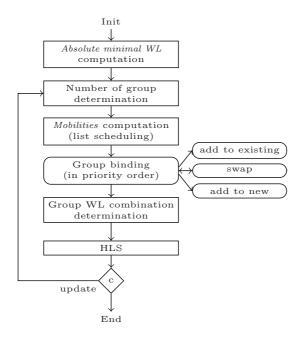

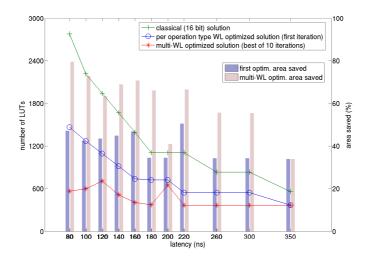

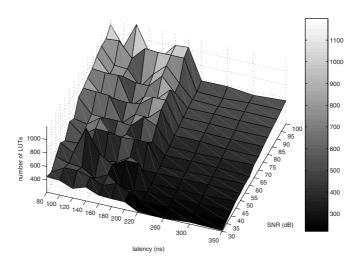

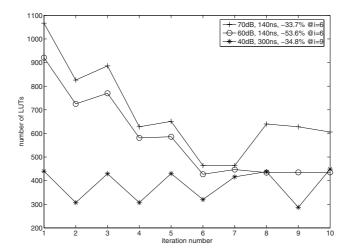

| About the Importance of Operation Grouping Procedures for Multiple Word-Length Architecture Optimizations           | 191 |

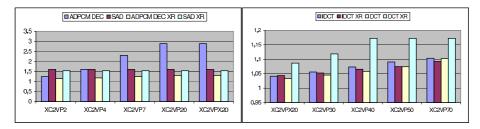

| Arithmetic [Regular Papers]                                                                                         |     |

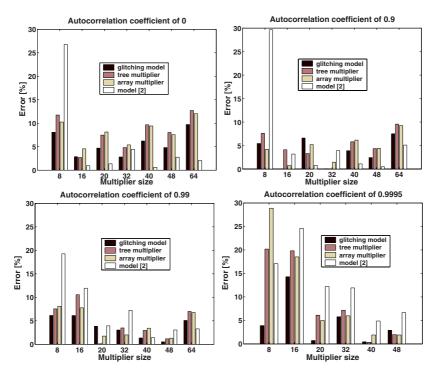

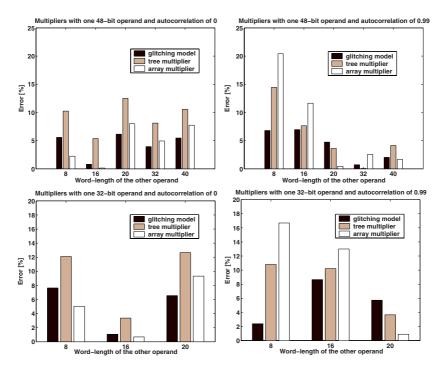

| Switching Activity Models for Power Estimation in FPGA Multipliers                                                  | 201 |

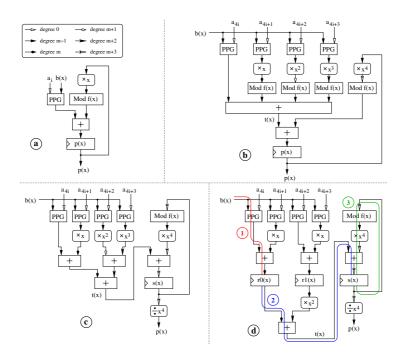

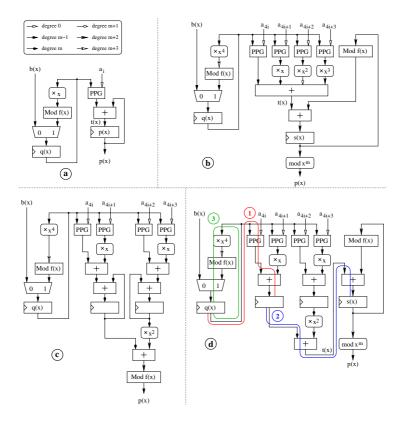

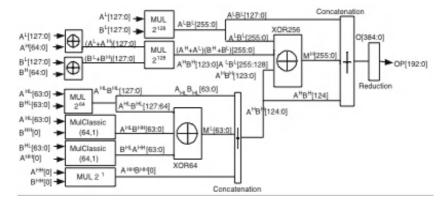

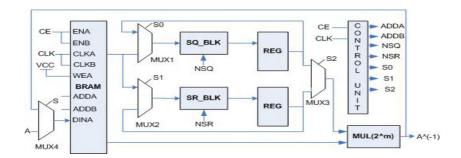

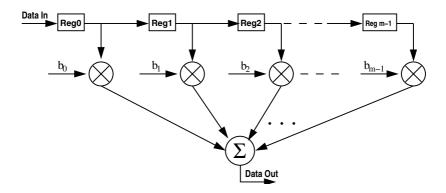

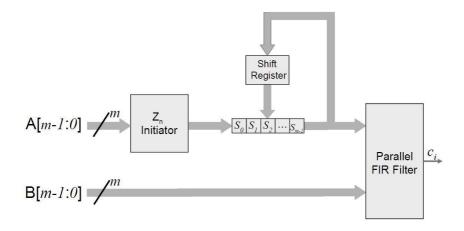

| Multiplication over $\mathbb{F}_{p^m}$ on FPGA: A Survey                                                            | 214 |

| Table of Contents                                                                                                          | XIII |

|----------------------------------------------------------------------------------------------------------------------------|------|

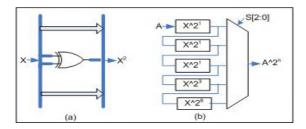

| A Parallel Version of the Itoh-Tsujii Multiplicative Inversion  Algorithm                                                  | 226  |

| A Fast Finite Field Multiplier                                                                                             | 238  |

| Applications [Regular Papers]                                                                                              |      |

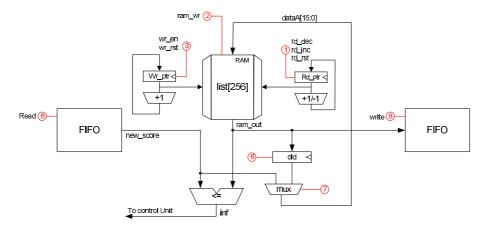

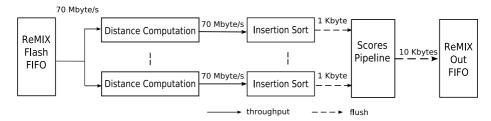

| Combining Flash Memory and FPGAs to Efficiently Implement a Massively Parallel Algorithm for Content-Based Image Retrieval | 247  |

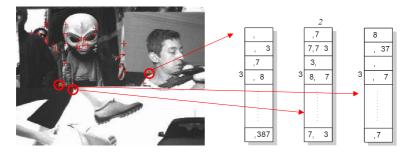

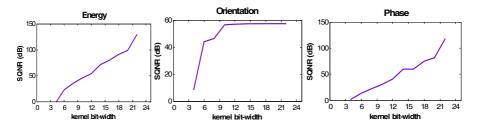

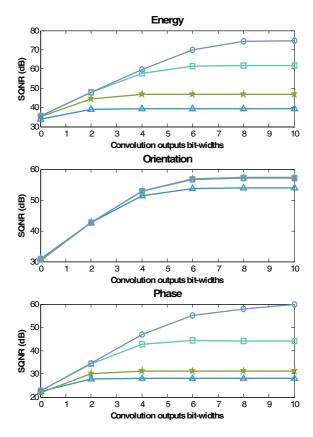

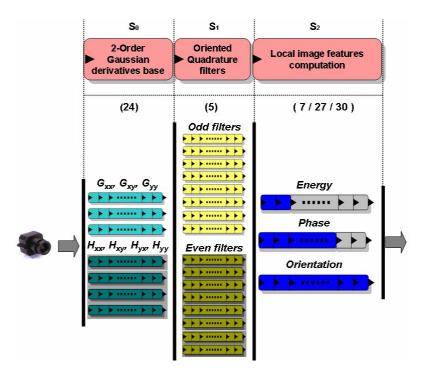

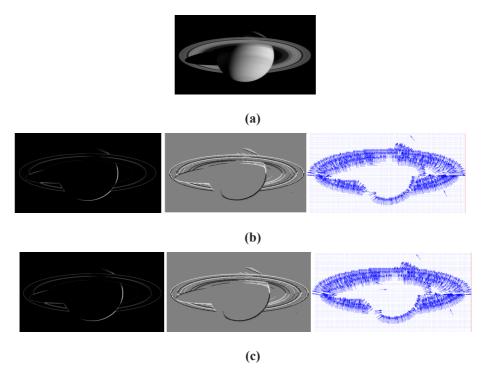

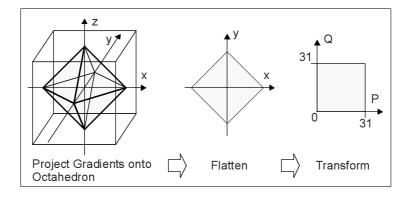

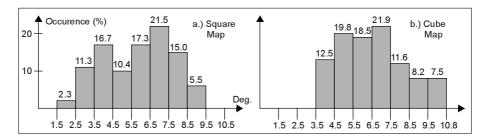

| Image Processing Architecture for Local Features Computation Javier Díaz, Eduardo Ros, Sonia Mota, and Richard Carrillo    | 259  |

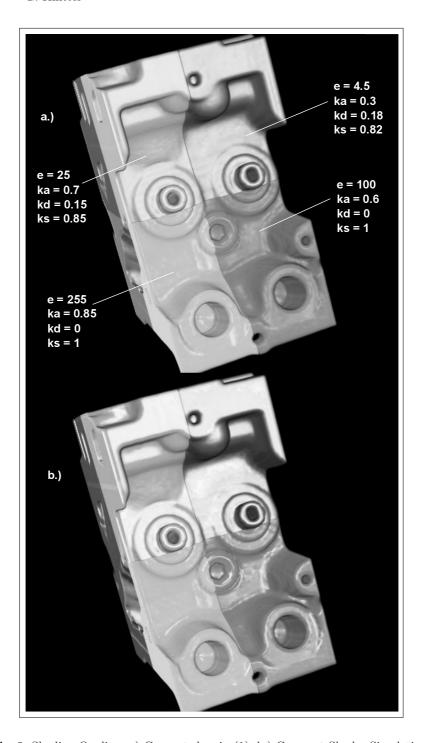

| A Compact Shader for FPGA-Based Volume Rendering Accelerators                                                              | 271  |

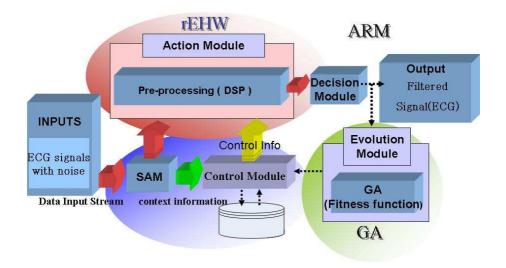

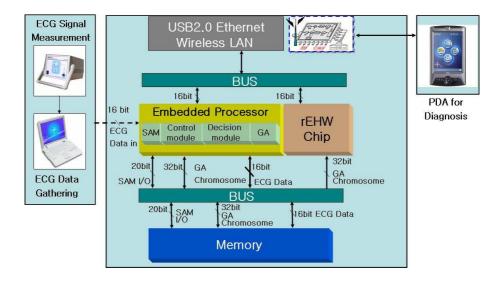

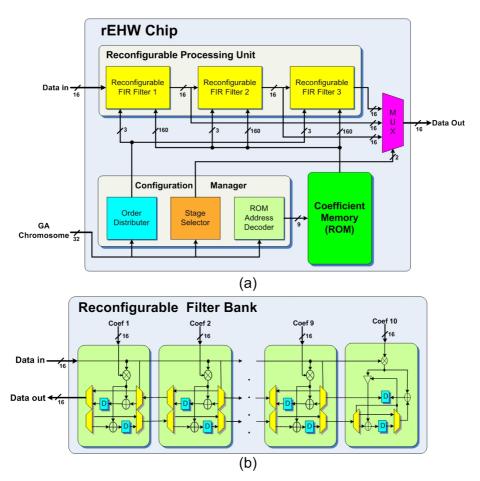

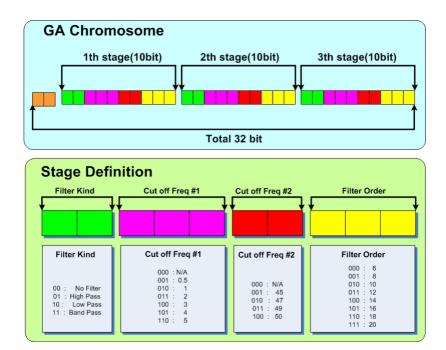

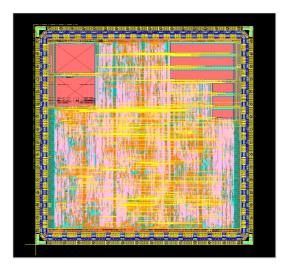

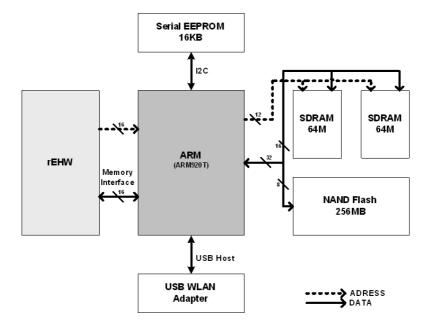

| Ubiquitous Evolvable Hardware System for Heart Disease Diagnosis Applications                                              | 283  |

| FPGA-Accelerated Molecular Dynamics Simulations: An Overview Xiaodong Yang, Shengmei Mou, and Yong Dou                     | 293  |

| Reconfigurable Hardware Acceleration of Canonical Graph Labelling  David B. Thomas, Wayne Luk, and Michael Stumpf          | 302  |

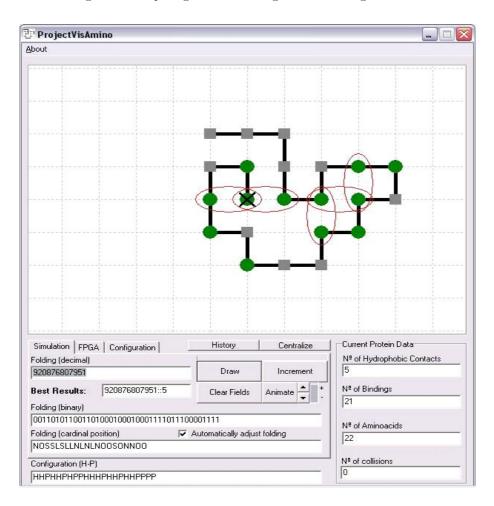

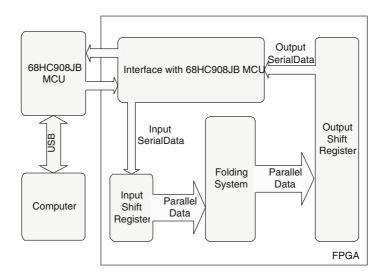

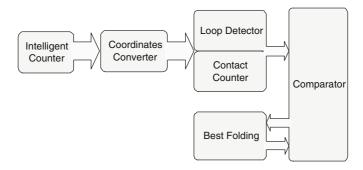

| Reconfigurable Computing for Accelerating Protein Folding Simulations                                                      | 314  |

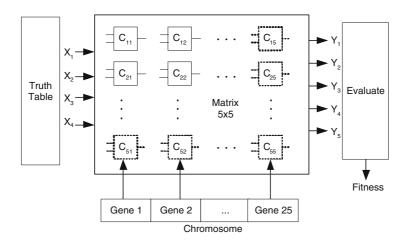

| Reconfigurable Parallel Architecture for Genetic Algorithms:  Application to the Synthesis of Digital Circuits             | 326  |

| Applications [Short Papers]                                                                                                |      |

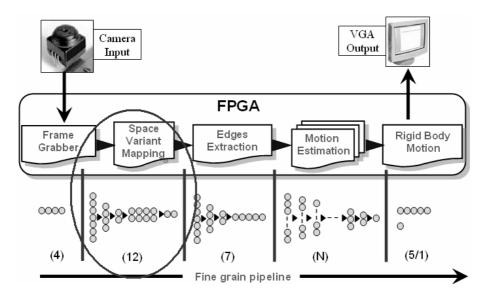

| A Space Variant Mapping Architecture for Reliable Car Segmentation                                                         | 337  |

# XIV Table of Contents

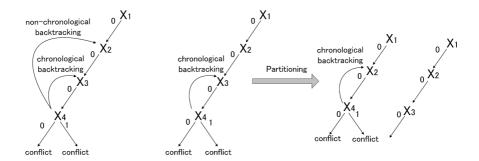

| A Hardware SAT Solver Using Non-chronological Backtracking and Clause Recording Without Overheads                                     | 343 |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| Searching the Web with an FPGA Based Search Engine                                                                                    | 350 |

| An Acceleration Method for Evolutionary Systems Based on Iterated Prisoner's Dilemma                                                  | 358 |

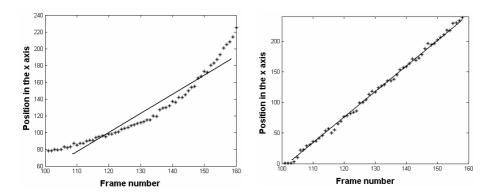

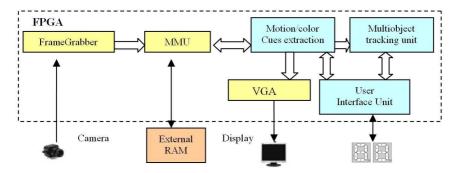

| Real Time Architectures for Moving-Objects Tracking                                                                                   | 365 |

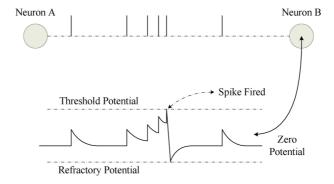

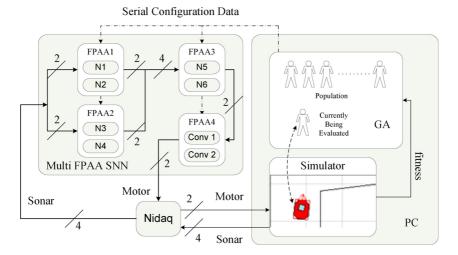

| Reconfigurable Hardware Evolution Platform for a Spiking Neural Network Robotics Controller                                           | 373 |

| Multiple Sequence Alignment Using Reconfigurable Computing Carlos R. Erig Lima, Heitor S. Lopes, Maiko R. Moroz, and Ramon M. Menezes | 379 |

| Simulation of the Dynamic Behavior of One-Dimensional Cellular Automata Using Reconfigurable Computing                                | 385 |

| Author Index                                                                                                                          | 391 |

# **Author Index**

| Amagasaki, Motoki 142          | Jevtic, Ruzica 201                      |

|--------------------------------|-----------------------------------------|

| Armstrong, Nilton B. (Jr.) 314 | Kanazawa, Kenji 358                     |

| D :                            | Kanstein, Andreas 1, 26                 |

| Benitez, César 385             | Kim, Hyun Dong 283                      |

| Berekovic, Mladen 1, 26        | Kim, Tae Seon 283                       |

| Bertels, Koen 130              | Knittel, Guenter 271                    |

| Beuchat, Jean-Luc 214          | 211                                     |

| Bispo, João 179                | Lee, Chong-Ho 283                       |

| Bollman, Dorothy 238           | Lee, Hanho 283                          |

| Bouwens, Frank 1               | Lee, Jae-Jin 85                         |

|                                | Lee, Je-Hoon 39                         |

| Caffarena, Gabriel 201         | Lee, Seung-Sook 39                      |

| Cardoso, João M.P. 179         | Lee, Yong-Min 283                       |

| Carreras, Carlos 201           | Lima, Carlos R. Erig 314, 326, 379, 385 |

| Carrillo, Richard 259, 337     | Lopes, Heitor S. 314, 326, 379, 385     |

| Chikhi, Rayan 247              | Luk, Wayne 302                          |

| Cho, Kyoung-Rok 39             | M 1 7 00                                |

| Choi, Chang-Seok 283           | Madsen, Jan 26                          |

| Cichaczewski, Ederson 326      | Maher, John 373                         |

| Cruz-Cortés, Nareli 226        | Mamagkakis, Stelios 91                  |

|                                | Maruyama, Tsutomu 358                   |

| Derrien, Steven 247            | Matsuyama, Kazunori 142                 |

| Díaz, Javier 259, 337, 365     | McElroy, Ciarán 350                     |

| Diniz, Pedro C. 97             | McGettrick, Séamas 350                  |

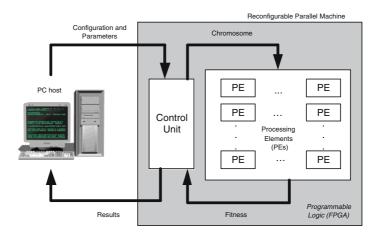

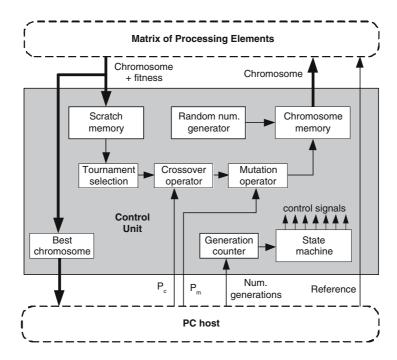

| Dong, Yazhuo 110               | McGinley, Brian 373                     |

| Dou, Yong 110, 155, 293        | Ménard, Daniel 191                      |

| Drimer, Saar 73                | Menezes, Ramon M. 379                   |

|                                | Min, Chul Hong 283                      |

| Ferlin, Edson P. 326           | Miyoshi, Takanori 214                   |

| Ferrer, Edgar 238              | Morales-Luna, Guillermo 226             |

|                                | Moreno, Oscar 238                       |

| Galuzzi, Carlo 130             | Morgan, Fearghal 373                    |

| Gauffriau, Adrien 167          | Moroz, Maiko R. 379                     |

| Gaydadjiev, Georgi 1           | Mota, Sonia 259, 337                    |

| Geraghty, Dermot 350           | Mou, Shengmei 293                       |

| Girau, Bernard 167             | Nakanishi, Masaki 343                   |

|                                | Nakashima, Yasuhiko 343                 |

| Hervé, Nicolas 191             | Nakayama, Hideaki 142                   |

| Hiramoto, Shinya 343           | Naous, Rawan 14                         |

| Hur, Jae Young 49, 61          | Noumsi, Auguste 247                     |

| Hwang, Dong-Guk 85             | ,                                       |

| Hwang, Seung-Gon 283           | Ohke, Yoshiharu 358                     |

| <del>-</del> :                 | Okamoto, Eiji 214                       |

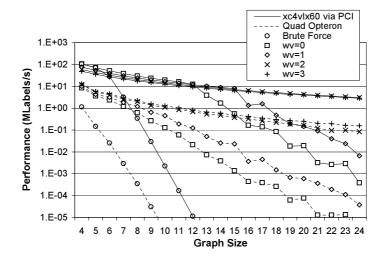

| Iida, Masahiro 142             | Oyama, Yoshihito 214                    |

|                                | -                                       |

Park, Jae-Hyun 283 Park, Joonseok 97

Quinton, Patrice 247

Rocke, Patrick 373 Rodriguez, Rafael 337 Rodríguez-Henríquez, Francisco 226 Ros, Eduardo 259, 337, 365

Saghir, Mazen A.R. 14 Saqib, Nazar A. 226 Scholz, Rainer 122 Sentieys, Olivier 191 Siozios, Kostas 91 Song, Gi-Yong 85 Soudris, Dimitrios 91 Sourdis, Ioannis 179 Stefanov, Todor 61 Stumpf, Michael 302 Sueyoshi, Toshinori 142 Thanailakis, Antonios 91 Thomas, David B. 302 Tomasi, Matteo 365 Torres-Huitzil, Cesar 167

Vassiliadis, Stamatis 49, 61, 130, 179

Weinert, Wagner R. 385 Wong, Stephan 49, 61 Wu, Guiming 155 Wu, Kehuai 26

Xu, Jinhui 155

Yamaguchi, Ryoichi 142 Yamaguchi, Yoshiki 358 Yamashita, Shigeru 343 Yang, Xiaodong 293

Zhou, Jie 110

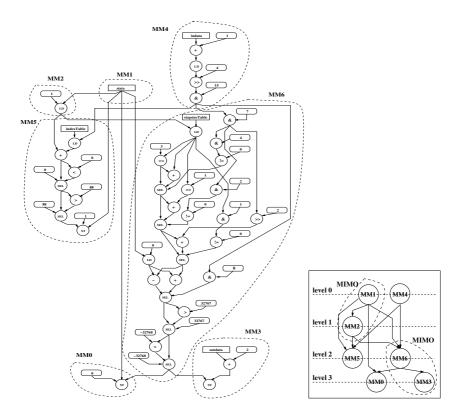

# Architectural Exploration of the ADRES Coarse-Grained Reconfigurable Array

Frank Bouwens<sup>1,3</sup>, Mladen Berekovic<sup>1,3</sup>, Andreas Kanstein<sup>2</sup>, and Georgi Gaydadjiev<sup>3</sup>

**Abstract.** Reconfigurable computational architectures are envisioned to deliver power efficient, high performance, flexible platforms for embedded systems design. The coarse-grained reconfigurable architecture ADRES (Architecture for Dynamically Reconfigurable Embedded Systems) and its compiler offer a tool flow to design sparsely interconnected 2D array processors with an arbitrary number of functional units, register files and interconnection topologies. This article presents an architectural exploration methodology and its results for the first implementation of the ADRES architecture on a 90nm standard-cell technology. We analyze performance, energy and power trade-offs for two typical kernels from the multimedia and wireless domains: IDCT and FFT. Architecture instances of different sizes and interconnect structures are evaluated with respect to their power versus performance trade-offs. An optimized architecture is derived. A detailed power breakdown for the individual components of the selected architecture is presented.

#### 1 Introduction

The requirements for higher performance and lower power consumption are becoming more stringent for newest generation mobile devices. Novel chip architectures should be able to execute multiple performance demanding applications while maintaining low power consumption, small area, non-recurring engineering costs and short time-to-market. IMEC develops a coarse-grained reconfigurable array (CGRA) called *Architecture for Dynamically Reconfigurable Embedded Systems* (ADRES) [1]. ADRES is a power efficient, but still flexible platform targeting 40MOPS/mW with 90nm technology. ADRES provides the designer with the tools to design an application specific processor instance based on an architecture template. This enables the designer to combine an arbitrary number of functional units, interconnects and register files.

The main contributions of the paper are:

A toolflow for energy, power and performance explorations of ADRES based CGRA architectures:

- A novel methodology for power analysis that replaces RTL simulation with instruction set simulation to obtain activity stimuli;

- Analysis of performance, power and energy tradeoffs for different array sizes and interconnect topologies;

- Derivation of an optimized architecture for key multimedia and wireless kernels and the power breakdown of its components.

This paper is organized as follows. Section 2 briefly introduces the ADRES architectural template. In Section 3 the toolflow and the developed power simulation methodology are presented. Section 4 contains the results of the architectural exploration experiments, the selection of the power/performance optimized instance and the detailed power breakdown of its components. Finally, the conclusions are presented in Section 5.

#### 2 ADRES Template

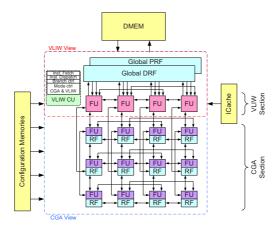

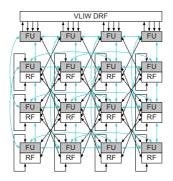

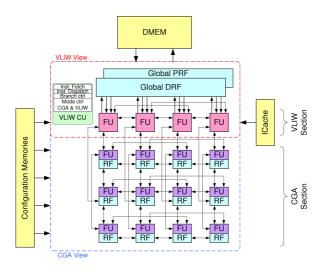

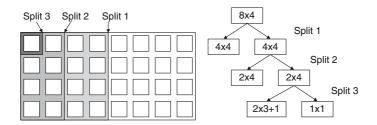

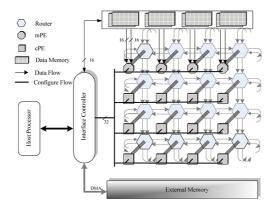

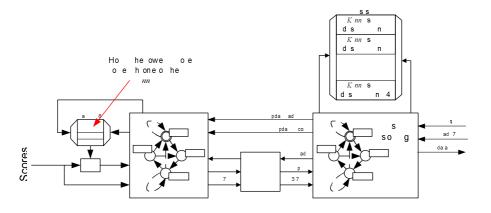

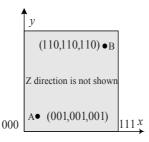

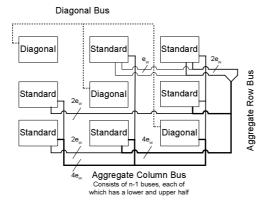

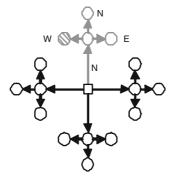

The ADRES architecture is a tightly-coupled architecture between two views: VLIW and CGA. Figure 1 shows an example of a 4x4 ADRES instance.

Fig. 1. ADRES Instance example

The VLIW control unit (CU) starts and stops the CGA loops when initiated by an CGA instruction in VLIW mode that works as a function call. It also accesses the instruction cache for the next instruction for the VLIW section and calculates the next Program Counter (PC).

The VLIW section in the example has an issue width of four instructions, while the CGA section has an issue width of 4 by 3 (12) instructions. The FUs in the VLIW view communicate through a multi-port global Data Register File (DRF), while those in the CGA use:

- global DRF;

- local register files (LRF);

- dedicated interconnects between the FUs.

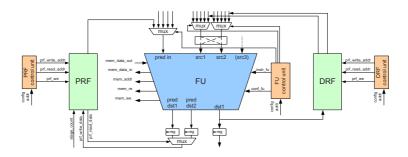

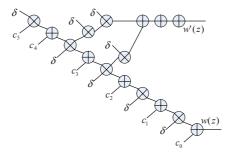

Example of the data path in ADRES is depicted in Figure 2. All FUs have 1 destination and 3 source ports at most. There are local Data and Predicate Register Files (PRF) used for storage of variables. The ADRES template is so flexible that it allows all, operation without local RFs, single local RF per FU or shared register files among several FUs [8].

Fig. 2. ADRES Data path example

#### 3 Tool Flow

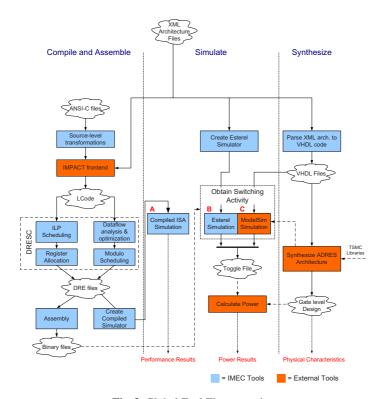

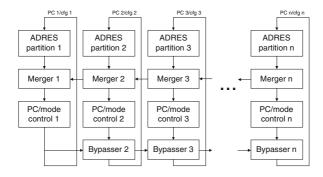

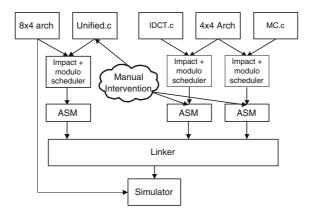

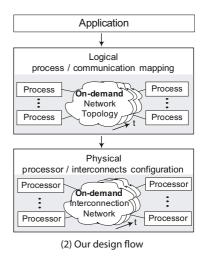

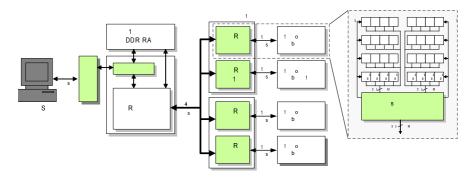

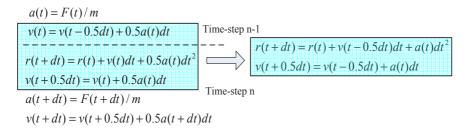

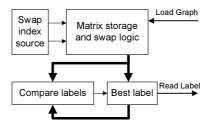

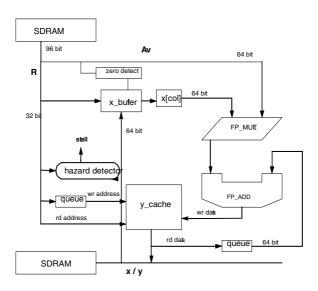

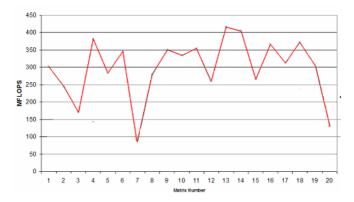

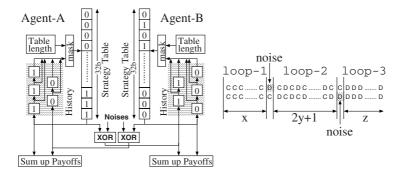

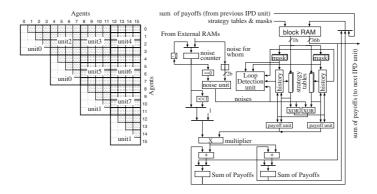

Figure 3 depicts the proposed tool flow for architectural exploration. It consist of basically three parts: 1) Compilation and Assembly providing binary files and a compiled instruction level simulator, 2) Synthesis providing gate level netlist and physical characteristics needed for power calculation and 3) Simulation to obtain power and performance figures.

The *Compile and Assemble* part transforms the ANSI-C application code into an optimized binary file. The code is first processed by the IMPACT [3] frontend that performs various ILP optimization and transforms it into an intermediate representation called Lcode. The DRESC2.0 compiler in Figure 3 reads the Lcode, performs ILP scheduling, register allocation and modulo scheduling for CGA mode and generates the optimized DRE files. These files are used to create a high level simulator which provides basic performance parameters such as instructions per cycle (IPC). In addition, the Assembler tool creates the binary files needed for the cycle true Esterel and ModelSim simulations.

The ADRES instance XML description is transformed into VHDL files and is synthesized in the *Synthesize* part. Synopsys *Physical Compiler v2004.12-SP1* [5] is used to create the netlist for 90nm CMOS library, from which area, capacitance and resistor values are extracted to be used multiple times.

In the *Simulate* part three different simulators are used. The compiled ISA simulator (marked as A in Figure 3) provides the performance numbers. ModelSim RTL simulator is used to simulate the generated RTL VHDL files at highest level of hardware accuracy

Fig. 3. Global Tool Flow overview

and to obtain the switching activity figures needed for RTL power calculations. The Esterel simulator [4] is based on the Esterel synchronous language dedicated to control-dominated reactive systems and models the entire ADRES instance as a state machine. The advantage of the Esterel simulator is the reduction in time to simulate a benchmark compared to ModelSim RTL simulations, as it is 8 - 12 times faster reducing overall time by a factor of 3 - 6.5 depending on the application. In addition, it is the behavior-level reference model for the core architecture available much earlier than the verified RTL.

Facilitated by its language, the Esterel simulator has the same structure as the actual implementation. Thus by enhancing it with bit toggle counting functions written in C, we are able of capturing the signal activity statistics of almost all relevant connections. This switching activity is what an RTL HDL simulator also generates for the power analysis tool. The match between the generated data is established by using the same signals as defined in the XML architecture description file.

The switching activities obtained after simulations are annotated on the gate level design created in the synthesize part. The toggling file and the gate level design are used by the *PrimePower v2004.12-SP1* of Synopsys [5] to estimate power.

For evaluation of the accuracy of the Esterel cycle accurate simulation versus the ModelSim VHDL simulation we used the IDCT kernel from MPEG. The IDCT benchmark is compiled for the VLIW only and for VLIW/CGA mode. The results are

|            | IDCT      | 1     |

|------------|-----------|-------|

|            | VLIW only | CGA   |

| Simulator  | (mW)      | (mW)  |

| ModelSim   | 46.5      | 59.16 |

| Esterel    | 57.75     | 65.65 |

| Difference | 24.2%     | 10.9% |

Table 1. Differences between Esterel and ModelSim for ADRESv0

depicted in the left column and in the right column of Table 1. The simulations are based on an non-pipelined ADRESv0 with a frequency of 100MHz.

From the results in Table 1 we can conclude that the proposed power simulation methodology with Esterel simulation works better in CGA mode that in VLIW mode. This is due to the fact that the CGA structure is captured by the simulator with more detail in the XML architecture file, while the VLIW part assumes a couple of implicit signals. Therefore the structure of the Esterel simulator and of the VHDL code match better for the CGA, resulting in more accurate signal switching statistics.

#### 4 Architecture Explorations

In this section we propose a variety of architectural options to create an ADRES instance. ADRES explorations were performed in [8] producing scheduling and area results only as [9] provides energy results of a 32-tap Complex FIR filter based on abstract energy models. Different architectures are composed from the architectural options and

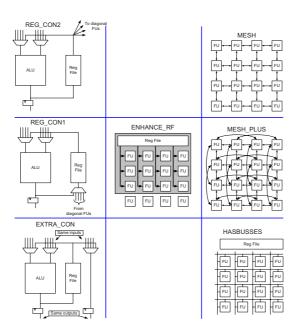

Fig. 4. Interconnection Options for Architectural Experiments

are evaluated for power, energy and performance. Finally, an optimized architecture is derived and a detailed power distribution for it is provided. This selection process utilizes two key benchmark kernels from multimedia and wireless application domains: IDCT and FFT. For the IDCT 396 8x8 block calculations are performed. For the FFT a single 1024 points FFT is performed. More benchmarks for evaluation were not available at the moment of writing.

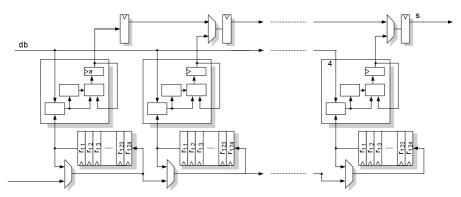

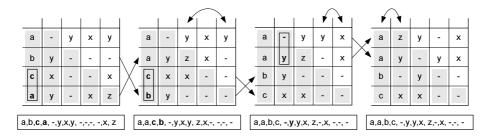

#### 4.1 Architecture Exploration Options

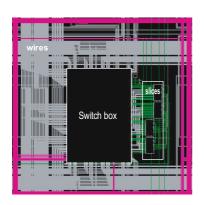

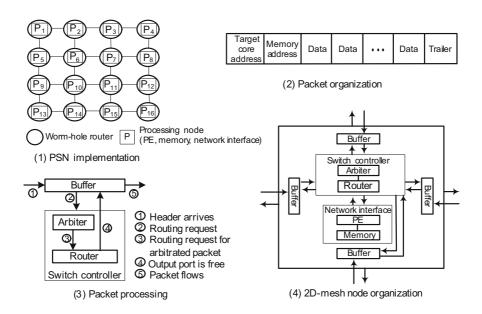

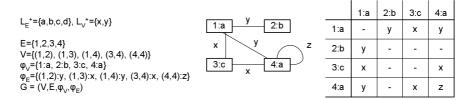

Fourteen different architectures are constructed from 7 different interconnection options as depicted in Figure 4. The architectures are described in the XML architecture file, which will be used in the tool flow described earlier. Exhaustive search of all configurations is impossible due to the large search space and required time.

The simplest interconnection option is mesh. It creates connections between destinations and sources of adjacent FUs in horizontal and vertical directions. The mesh\_plus interconnection is an extension of mesh with additional connections that routes over the neighboring FUs. The reg\_con1 and reg\_con2 options create diagonal connections between neighboring FUs and RFs. This creates additional routing and the possibility of data sharing among FUs connecting directly to the RFs. The difference is that reg\_con1 receives data from its neighbors while reg\_con2 sends data to them. The extra\_con option offers an extra FU bypass to enable parallel processing and routing. The enhance of option has shared read and write data ports from the global DRF to the vertically connected FUs as proposed by Kwok et al. [2]. This is beneficial for communication as the global DRF is used as communication medium in the array, however it increases power consumption due to the frequent accesses to the global DRF. Splitting up the powerhungry DRF into smaller, local DRFs was one of the main features of power reduction [6]. The option has\_busses determines if predicate and data busses of 1 and 32 bits wide respectively are implemented in the design. By combining various interconnection options 14 different architectures are created as noted in Table 2.

| Architecture | mesh | mesh | reg  | reg  | extra | enhance | has    |

|--------------|------|------|------|------|-------|---------|--------|

|              |      | plus | con1 | con2 | con   | RF      | busses |

| mesh         | X    |      |      |      |       |         |        |

| mesh_plus    | X    | X    |      |      |       |         |        |

| xtra_con     | X    | X    |      |      | X     |         |        |

| reg_con1     | X    | X    | X    |      |       |         |        |

| reg_con2     | X    | X    |      | X    |       |         |        |

| reg_con_all  | X    | X    | X    | X    |       |         |        |

| enh_rf       | X    | X    |      |      |       | X       |        |

| busses       | X    | X    |      |      |       |         | X      |

| arch_1       | X    | X    |      | X    | X     | X       |        |

| arch_2       | X    | X    | X    |      | X     | X       |        |

| arch_3       | X    | X    |      | X    |       | X       |        |

| arch_4       | X    | X    | X    |      |       | X       |        |

| all          | X    | X    | X    | X    | X     | X       | X      |

| ref          | X    | X    | X    |      | X     | X       | X      |

**Table 2.** Architectural Exploration Selection Options

The physical properties of RFs and FUs are the same for all architectures. The local and global RFs have 16 and 64 words, respectively. The data bus width between DRFs, external memories and FUs is 32-bits. Each FU is capable of regular additions and multiplications of which only the FUs in the VLIW section are capable of load/store operations. The store capabilities of the FUs requires 12 read and 4 write ports for the global DRF. The global PRF has 4 read and write ports. The local DRFs have 2 read and 1 write ports and the local PRFs have 1 read and write port. The configuration memories (CM) are of fixed 128 words depth to store the benchmark configurations for the CGA. The CMs' bus sizes are variable and each FU, RF and multiplexor has its dedicated memory. We use standard 90nm general purpose libraries for both the standard cells and the memories.

The modeled non-pipelined architectures assume zero cache miss data memories and zero miss instruction cache. The external busses, the data memory and the I-cache are not considered in our power estimation study. However, the configuration memory, which serves as an instruction memory for the array mode, is considered in the CM module.

#### 4.2 Instance Selection

The FFT and IDCT benchmarks are used to select the appropriate instance based on power, energy and performance trade-offs. As a comparison base a non-pipelined scalar RISC architecture is modeled as an array of size  $1x1 (np\_1x1\_reg)$ .

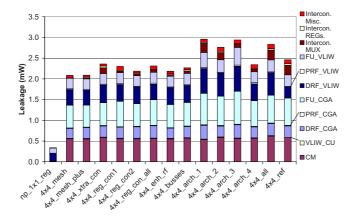

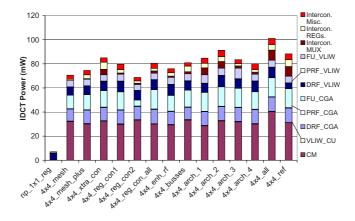

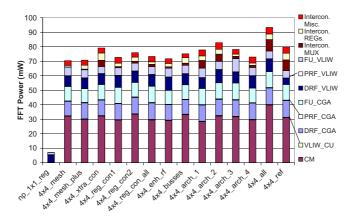

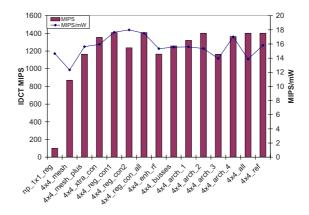

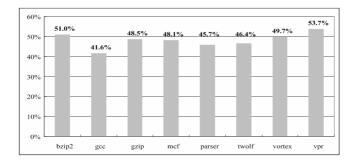

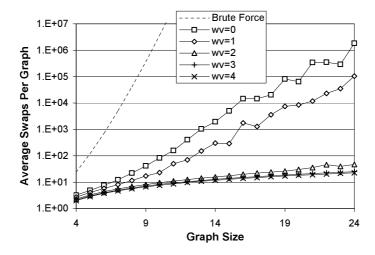

Figure 5 presents the leakage power results of the architectures. The 4x4\_all has high leakage due to the all interconnect options in Table 2. The Synopsys synthesis tool is not always consistent as the leakage power of 4x4\_ref is significantly reduced compared to 4x4\_arch\_1. Figures 6 and 7 present the total power results for the two benchmarks. The order of components in the legends are the same in the charts of which PRF\_CGA, PRF\_VLIW and VLIW\_CU are negligible. The following components are separately measured and divided in CGA and VLIW parts. There is a data register file DRF, predicated register file PRF, functional units FU and configuration memory CM.

Fig. 5. Leakage Power

Fig. 6. IDCT Power @ 100MHz

Fig. 7. FFT Power @ 100MHz

Fig. 8. IDCT Performance @ 100MHz

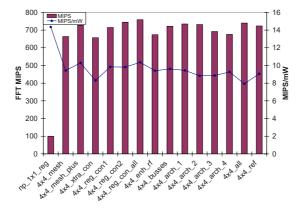

Fig. 9. FFT Performance @ 100MHz

The register files (PRF and DRF) in VLIW mode are global while in CGA mode the sum of all local register files is considered. The 4x4\_all option consumes highest total power compared to the other options mainly due to the large amount of interconnections requiring larger CMs.

We measured the performance in MIPS using the number of executed instructions obtained from the compiled instruction set simulator divided by the total number of execution cycles. The resulting performance charts are depicted in Figures 8 and 9. The  $np\_lxl\_reg$  shows a low MIPS result, but yet gives a high MIPS/mW. The performance charts also show that the fully interconnected architecture  $4x4\_all$  is not an efficient option. The bypass feature in  $4x4\_xtra\_con$  has some advantage for IDCT only, but certainly not for FFT. This is an typical application that accesses DRFs quite often, which is shown in Figure 9 by  $4x4\_enh\_rf$  and  $4x4\_reg\_con\_all$  having a higher MIPS/mW factor compared to  $4x4\_xtra\_con$ . The presence of busses in the design does not give much advantages, since it requires additional multiplexors, larger CMs and data networks, that all increase power.

Fig. 10. IDCT Energy-Delay @ 100MHz

Fig. 11. FFT Energy-Delay @ 100MHz

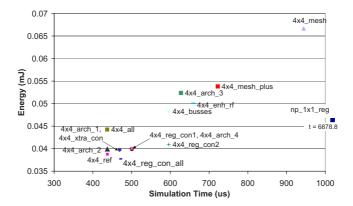

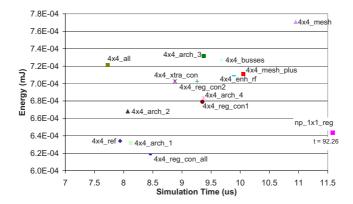

The power and performance charts are a good indication for selection of the appropriate architecture, however the energy vs runtime shown in Figures 10 and 11 is of more significance.

The *np\_lx1\_reg* architecture does not have the highest energy consumption, however it is about 8 times slower than the *4x4\_mesh* architecture. Of all considered 4x4 arrays the *4x4\_mesh* has the highest energy consumption for both benchmarks. The *4x4\_reg\_con\_all* has the lowest energy consumption for both benchmarks, but it is not the fastest option, which is *4x4\_all*. The *4x4\_ref* architecture is a good alternative between energy and performance results.

We select the architecture with the lowest energy consumption and reasonable performance, which can be seen from the energy-delay charts is  $4x4\_reg\_con\_all$ . The  $4x4\_reg\_con\_all$  interconnection architecture consists of a *mesh* and *mesh* plus interconnection topology and diagonal connections via multiplexors between FUs and local and global RFs as depicted in Figure 12.

Fig. 12. Proposed ADRES Instance

#### 4.3 Power Breakdown

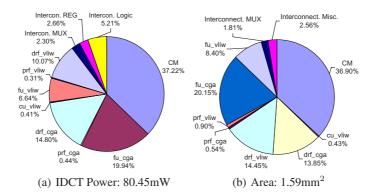

The power and performance figures of the proposed ADRES instance are summarized in Table 3. The detailed power and area breakdown for IDCT are depicted in Figure 13. The components with \_vliw postfix are located in the VLIW section and are operational in both VLIW and CGA mode, while those with the \_cga postfix are located in the CGA section.

|      | Total |        | MIPS | MIPS/mW | mW/MHz |

|------|-------|--------|------|---------|--------|

|      | Power | Energy |      |         |        |

|      | (mW)  | (uJ)   |      |         |        |

| FFT  | 73.28 | 0.619  | 759  | 10.35   | 0.7328 |

| IDCT | 80.45 | 37.72  | 1409 | 17.51   | 0.8045 |

Table 3. Characteristics of 4x4\_reg\_con\_all

The power chart in Figure 13(a) shows that the CMs, FUs and DRFs consume most of the power. Interesting to note is the low power consumption of less than 10% of the interconnections between modules as opposed to 10 - 30% that where reported for regular DSP design [7]. The VLIW control unit (cu\_vliw) and PRFs consume the least amount of power as these are the smallest components.

Fig. 13. Power and Area distribution 4x4\_reg\_con\_all @ 100MHz

The area chart in Figure 13(b) shows that the CMs, FUs and DRFs require most area. The CMs have a fixed depth of 128 words during the architectural explorations.

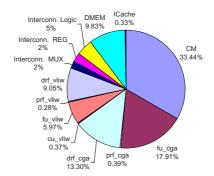

The power measurements of ADRES were based on the core architecture only. To get a power prediction of the complete ADRES processor including instruction cache and data memories we simulated the activities of these blocks. For the IDCT the data memories were activated for 100% of the cycles and the instruction cache for 4.3% respectively. According to the data sheets of SRAM memory models this results in a power consumption of 0.03mW/MHz for the data memories and 0.05 mW/MHz for

the instruction cache. The power consumption of the not activated memory modules is negligible and assumed as zero. The distribution of all the components in the processor for the IDCT benchmark is shown in Figure 14. It shows that in addition to the FUs,

Fig. 14. Overview of ADRES Processor Power Consumption with IDCT

DRFs and CMs, the data memory (DMEM) consumes significant amount of power. The I-cache power consumption is negligible.

The experiments were obtained utilizing the non-pipelined version ADRESv0, however, a pipelined version ADRESv1 is under development at the moment. Preliminary results are encouraging reaching the performance target of 40MOPS/mW. The reconfigurable architecture Morphosys [10] is comparable to ADRES, but does not provide power results of IDCT and FFT. No other comparable architectures are know at the moment of writing.

#### 5 Conclusions

In this paper we explored various architectures for the ADRES coarse-grained reconfigurable array and selected the appropriate one based on power, energy and performance trade-offs. An especially defined methodology and tool flow 1) maps the FFT and IDCT benchmarks on the array using the DRESC compiler for high performance, low energy execution, 2) synthesizes each architecture into a front-end design and 3) simulates with either the compiled ISA simulator, ModelSimv6.0a or the Esterel simulator for performance and power evaluations. Power is calculated by annotating the switching activity after Esterel or RTL simulation onto the gate-level design. Our three-fold simulation approach permits to obtain results quickly, which is important for architecture exploration.

Fourteen different ADRES instances were created based on 7 different architectural features and evaluated with the available tool flow. The obtained power, energy and performance charts show that a combination of mesh and mesh plus interconnection topologies with diagonal connections between functional units and local data register files results in good performance of 10.35 - 17.51 MIPS/mW and power of 73.28 - 80.45mW with the least amount of energy 0.619 - 37.72uJ for FFT and IDCT, respectively.

#### References

- Bingfeng Mei, Serge Vernalde, Diederik Verkest, Hugo De Man and Rudy Lauwereins: ADRES: An Architecture with Tightly Coupled VLIW Processor and Coarse-Grained Re-configurable Matrix, IMEC, 2003, Kapeldreef 75, B-3001, Leuven, Belgium, DATE 2004

- Zion Kwok and Steven J. E. Wilton: Register File Architecture Optimization in a Coarse-Grained Reconfigurable Architecture, University of British Columbia, April 2005, 35–44, Proceedings of the 13th Annual IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM'05) - Volume 00

- 3. The IMPACT Group. http://www.crhc.uiuc.edu/Impact/

- 4. http://www-sop.inria.fr/esterel-org/

- 5. http://www.synopsys.com/

- Bingfeng Mei: A Coarse-Grained Reconfigurable Architecture Template and its Compilation Techniques, Katholieke Universiteit Leuven, Januari 2005, ISBN: 90-5682-578-X

- Renu Mehra and Jan Rabaey: Behavioral Level Power Estimation and Exploration, April 1994, Proc. First International Workshop on Low Power Design, University of California at Berkeley

- 8. Bingfeng Mei, Andy Lambrechts, Jean-Yves Mignolet, Diederik Verkerst and Rudy Lauwereins: *Architecture Exploration for a Reconfigurable Architecture Template*, March 2005, IEEE Design & Test of Computers, IMEC and Katholieke Universiteit Leuven

- Andy Lambrechts, Praveen Raghavan and Murali Jayapala: Energy-Aware Interconnect-Exploration of Coarse Grained Reconfigurable Processors, 4th Workshop on Application Specific Processors (WASP), September 2005

- Hartej Singh, Ming-Hau Lee, Guangming Lu, Fadi J. Kurdahi and Nader Bagherzadeh: MorphoSys: an integrated reconfigurable system for data-parallel and computation-intensive applications, University of California (US) and Federal University of Rio de Janeiro (Brazil), May 2000, 465 481, IEEE Transactions on Computers

# A Configurable Multi-ported Register File Architecture for Soft Processor Cores

Mazen A.R. Saghir and Rawan Naous

Department of Electrical and Computer Engineering American University of Beirut P.O. Box 11-0236 Riad El-Solh, Beirut 1107 2020, Lebanon {mazen,rsn11}@aub.edu.lb

Abstract. This paper describes the architecture of a configurable, multi-ported register file for soft processor cores. The register file is designed using the low-latency block RAMs found in high-density FPGAs like the Xilinx Virtex-4. The latency of the register file and its utilization of FPGA resources are evaluated with respect to design parameters that include word length, register file size, and number of read and write ports. Experimental results demonstrate the flexibility, performance, and area efficiency of our proposed register file architecture.

#### 1 Introduction

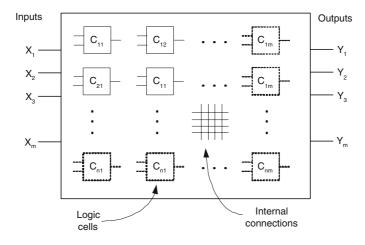

Growing interest in configurable and reconfigurable computing has increased the proportion of field programmable gate arrays (FPGAs) being used to implement computational platforms. High logic densities and rich on-chip features, such as hardware multipliers, memory blocks, DSP blocks, peripheral controllers, and microprocessor cores, make it possible to quickly implement highly tuned system designs that couple software programmable processor cores with custom hardware blocks that can be implemented inside the logic fabric of an FPGA.

The past few years have also witnessed the emergence of *soft* processor cores [1,2]. These processors are specified in a hardware description language, such as VHDL or Verilog, and implemented in the logic fabric of an FPGA. The main advantages of soft processors are that their datapaths can be easily reconfigured and their instruction set architectures extended to support user-defined machine instructions. To overcome the performance and area inefficiencies of implementing soft processors in FPGAs, the microarchitectures of these processors are typically optimized to make use of available on-chip resources [3]. For example, a common optimization is to use embedded memory blocks to implement register files [4]. Given the simplicity of current soft processor architectures, these register files typically feature two read ports and one write port. However, as the complexity of soft processor cores increases to support wider instruction issue [5,12], multithreading [6], and customized datapaths [7] flexible register file architectures capable of supporting multiple read and write ports are needed.

In this paper we describe the architecture of a configurable, multi-ported, register file for soft processor cores. We also evaluate the performance of our

Fig. 1. A register file with four read and two write ports

design and measure its utilization of FPGA resources. In Sect. 2, we describe the architecture of our register file and highlight the characteristics and limitations of its design. Then, in Sect. 3 we describe how we evaluate the performance and area of the register file. Next, in Sect. 4, we analyze the effects of various register file design parameters such as data word length, register size, and number of read/write ports on both the latency and area of the register file. Then, in Sect. 5, we show how our register file can be used to customize the datapath of a soft VLIW processor and how this affects the overall performance and area of the processor. In Sect. 6, we describe related work and compare it to our own. Finally, in Sect. 7, we provide our conclusions and describe future work.

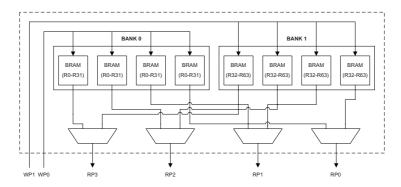

# 2 Multi-ported Register File Architecture

Our register file is designed around the embedded block RAMs (BRAMs) found in contemporary, high-density, FPGAs such as the Xilinx Virtex-4 [8]. The BRAMs on the Virtex-4 are dual-ported, synchronous, memory blocks capable of storing 16,384 data and 2,048 parity bits that can be organized in various aspect ratios. The two ports are independent and can each be configured as either a read or a write port. In our design, each BRAM is configured as a  $512 \times 36$ -bit memory block with one read port and one write port, and this configuration forms the basic building block in our register file. Figure 1 shows how eight such BRAMs can be used to implement a  $64 \times 32$ -bit register file with four read and two write ports.

The key to supporting multiple register ports is to organize the BRAMs into register banks and duplicate data across the various BRAMs within each bank. The register banks are each used to store a *subset* of the register file. In Fig. 1, the BRAMs are divided into two register banks used to store registers R0 to R31 and R32 to R63, respectively. Since register banks hold mutually exclusive sets of registers, they can be updated independently. Associating each register bank with a separate write port provides support for multiple write ports.

Within each register bank, multiple BRAMs are used to store duplicate copies of the corresponding register subset. By duplicating register values across BRAMs, the values of different registers can be read from different BRAMs simultaneously, thus providing support for multiple read ports. Since the register file in Fig. 1 has four read ports, each register bank contains four BRAMs that store duplicate copies of the corresponding register subset. Since each register bank stores a different subset of the register file, multiplexers are used to provide access to the registers stored in each register bank. In Fig. 1, four multiplexers – one for each read port – are used to provide access to all the registers in both register banks. Finally, to maintain data consistency among the BRAMs in a register bank, each BRAM is connected to the corresponding register write port making it possible to update all BRAMs simultaneously.

#### 2.1 Design Characteristics and Limitations

A major characteristic of our register file is that it is fully configurable and can be designed with an *arbitrary* word length, register size, and number of read or write ports. Here it is worth noting that the number of register ports does not have to be even or a power of two. This enables customizing the register file at a very fine level to the specific needs of the target processor microarchitecture. However, the size of the register subset associated with a register bank must be a power of two, and this causes some register file configurations to have register banks with different sized register subsets. For example, a register file of size 64 with five read ports and three write ports will consist of three register banks, two of which containing 16 registers and one containing 32 registers. However, such an asymmetric distribution of register subsets does not affect the performance, area, or functionality of the register file.

Another characteristic of our register file is that it influences the way registers and instructions get allocated and scheduled, respectively. Since registers are distributed across several banks associated with different write ports, registers must be allocated, and instructions scheduled, in a manner that avoids contention for the write ports. Thus, instructions cannot be scheduled to execute in parallel if they produce results in registers that belong to the same register bank. Although various software and hardware techniques, such as register renaming, can be applied to solving this problem [9,10], these techniques and their effects are beyond the scope of this paper.

Finally, our register file is limited by the number and size of the BRAMs available within the FPGA. If WL and DW are the word length and data width of the register file and BRAMs, respectively, implementing a register file with M read ports and N write ports requires  $\lceil WL/DW \rceil \times M \times N$  BRAMs distributed across N banks. Since BRAMs typically have a fixed size and can only be configured in a limited number of aspect ratios, there is a limit on the number of registers that can be stored within each BRAM. In the Xilinx Virtex-4 FPGA, the BRAM aspect ratio that corresponds to the maximum word length is  $512 \times 36$  bits. This limits the size of the register subset that can be stored in

a BRAM to 512 registers. Although this limit can be easily extended by using more BRAMs in each register bank, we do not consider this case in this paper.

#### 3 Performance and Area Evaluation

To evaluate the performance and area of our register file architecture, we developed a parameterizable register file generator called MPRFGen. MPRFGen reads design parameters such as word length, register size, and number of read and write ports and generates the corresponding VHDL code, which instantiates the appropriate number of BRAMs and organizes them as a multi-ported register file. Once the VHDL code is generated, we use the Xilinx ISE 8.2.03i tools, targeting a Xilinx Virtex-4 LX (XC4VLX160-12FF1148) FPGA, to synthesize and implement the register file. We chose the XC4VLX160 as our target FPGA because of its high logic density, which is representative of the types of FPGAs used for implementing computational platforms designed around soft processor cores, and because it contains 288 BRAMs, which is large enough to implement and evaluate a wide range of register file organizations. Finally, we used the Xilinx Timing Analyzer tool to measure the latency of the register file and the post-place-and-route synthesis reports to measure its utilization of FPGA resources. Although somewhat crude, the number of BRAMs and FPGA slices used to implement a register file is still an accurate measure of its area.

#### 3.1 Register File Latency

The latency of the register file is determined by its critical path delay as reported by the timing analyzer tool. The critical path delay can be generally expressed by the following equation:

Critical Path Delay =

$$T_{\text{bram}} + T_{\text{routing}} + T_{\text{mux}}$$

(1)

Here,  $T_{\rm bram}$  is the latency of a BRAM block,  $T_{\rm routing}$  is the routing delay along the critical path between the corresponding register bank and output multiplexer, and  $T_{\rm mux}$  is the delay of the output multiplexer. Typically,  $T_{\rm bram}$  is a constant that depends on the fabrication process technology and speed grade of the FPGA. For the Xilinx XC4VLX160-12FF1148,  $T_{\rm bram}=1.647$  ns. On the other hand,  $T_{\rm routing}$  and  $T_{\rm mux}$  depend on the organization of the register file and vary with word length and the number of read and write ports. Both delays also depend on the architecture of the FPGA routing network and the efficiency of the placement and routing tool. In Sect. 4, we examine how various design parameters affect the latency and FPGA resource utilization of our register file architecture.

# 4 Results and Analysis

In this section we present the results of three experiments we conducted to assess the impact of word length, register file size, and the number of read and

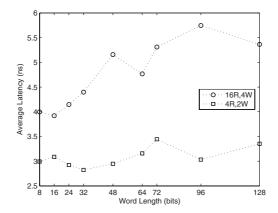

Fig. 2. Latency vs. word length

write ports on both the latency and FPGA resource utilization of our register file architecture. To minimize the effect of the place-and-route tool on latency measurements, we report the *average latency* for each register file organization, which we compute based on *nine* latency measurements corresponding to different starting placer cost tables [11]. We also report FPGA resource utilization in terms of the number of BRAMs and slices used to implement each register file.

#### 4.1 Effect of Word Length

Our first experiment examined the impact of register word length on the latency and area of two register files configured with 16 read and 4 write ports and 4 read and 2 write ports, respectively. Figure 2 shows the latencies of both register files as the word length is increased from 8 to 128 bits. Our results show that latency tends to increase with word length since the amount of routing used to connect register banks to output multiplexers also increases with word length. The additional routing delays cause  $T_{\rm routing}$  to increase, and this causes overall latency to increase. However, our results also suggest that the latency is sensitive to variations in placement and routing. In Fig. 2, the latencies associated with some word lengths are actually lower than those associated with smaller word lengths. Finally, our results show that the impact of word length becomes more pronounced as the number of register ports increases. This is due to the corresponding increase in routing resources needed to connect register banks to output multiplexers, which is also proportional to the product of the number of read and write ports.

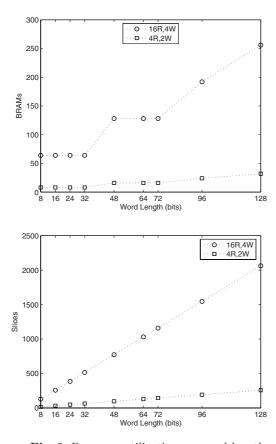

Figure 3 shows the utilization of FPGA resource as a function of word length for both register files. In Sect. 3 we saw that the number of BRAMs used to implement a register file depends on the word length, the data width of the BRAM, and the number of read and write ports. Figure 3 shows that, for each register file, the number of BRAMs increases in steps that track the ratio of the register word length to BRAM data width. Figure 3 also shows that the number

Fig. 3. Resource utilization vs. word length

of FPGA slices used to implement the register file is a linear function of its word length. This is due to the fact that slices are only used to implement output multiplexers and that the number of slices needed to implement a register file is proportional to the product of word length by the number of read ports.

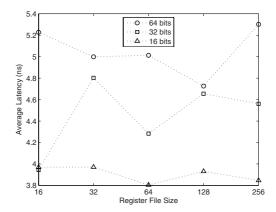

#### 4.2 Effect of Register File Size

Our second experiment examined the impact of register file size. For this experiment we used three register files that were each configured with 16 read ports and 4 write ports, and that had word lengths of 16-, 32-, and 64-bits, respectively. Figure 4 shows the average latencies of the three register files as we increased the size of the register file from 16 to 256.

Our results show that there is little correlation between the size of a register file and its latency. As the size of the register file increases, additional addressing lines are needed for each of its read and write ports, and the number of registers allocated to each bank increases. Routing the additional addressing lines can introduce some variation in the latency of different sized register files, but these

Fig. 4. Latency vs. register file size

Table 1. FPGA resource utilization for a register file with 16 read and 4 write ports

| Word Length | $\mathbf{BRAMs}$ | Slices |

|-------------|------------------|--------|

| 16-bits     | 64               | 257    |

| 32-bits     | 64               | 515    |

| 64-bits     | 128              | 1,031  |

variations are mainly due to the effects of placement and routing. Moreover, the increase in the number of registers per bank is typically absorbed by the BRAMs, which can each store up to 512 registers. As a result, even if the size of the register file increases, its organization – the number of its BRAMs, register banks, output multiplexers, and the data paths used to connect them – does not change. This leads us to conclude that the latency of a register file is independent of its size, and that the variations in the latencies of different sized register files that otherwise have the same organization are mainly due to the effects of placement and routing. Of course, if more than 512 registers per bank are needed, additional BRAMs will be required, and this will effect both the organization and the latency of the register file. However, since we have assumed that this limit will not be exceeded, we do not consider this case any further. Finally, since the organization of a register file does not change with its size, it follows that the area occupied by the register file also does not change. Table 1 shows the utilization of FPGA resources for each of the register files used in this experiment. As we increase the size of each register file, its utilization of FPGA resources remains unchanged.

#### 4.3 Effect of Read/Write Ports

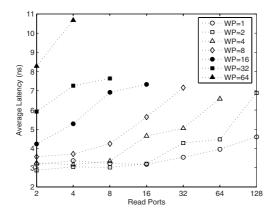

Our third experiment examined the impact of the number of register read and write ports. For this experiment we used a  $256 \times 32$ -bit register file and varied the number of its read ports from 2 to 128 and the number of its write ports from

Fig. 5. Latency vs. number of read and write ports

1 to 64. Since our target FPGA, the Xilinx XC4VLX160, contains 288 BRAMs, we only considered register file configurations whose BRAM requirements could be accommodated by the FPGA.

Figure 5 shows the average latency of the register file as a function of its read and write ports<sup>1</sup>. As expected, our results show that latency increases with the number of read and write ports. This reflects the architecture of our register file where the width of the output multiplexers – the number of inputs to select from – depends on the number of register banks, which, in turn, depends on the number of write ports. Since output multiplexers are implemented as a hierarchy of lookup tables and two-input multiplexers, the depth of the hierarchy and the corresponding delay,  $T_{\rm mux}$ , increase as the width of the output multiplexers increases. Moreover, as the number of register banks increases, more routing resources are used to connect the register banks to the output multiplexers, causing  $T_{\rm routing}$  to also increase. Similarly, increasing the number of read ports increases the number of output multiplexers and the amount of routing needed to connect the register banks to the output multiplexers, and this also increases  $T_{\rm routing}$ . The latency of a register file therefore increases in proportion to the product of the number of read and write ports.

Figure 6 shows the utilization of FPGA resources as a function of read and write ports. In Sect. 3 we saw that BRAM utilization is proportional to the product of the number of read and write ports. Similarly, the utilization of FPGA slices depends on the width of the output multiplexer, which determines the number of slices needed to implement the multiplexer. The number of slices used to implement the register file is proportional to the product of the number of read and write ports.

Having gained some insight into the effects of various register file design parameters on latency and area, we next examine how our register file can be used

<sup>&</sup>lt;sup>1</sup> Write ports are labeled WP on the graphs.

Fig. 6. Resource utilization vs. number of read and write ports

to customize the datapath of a soft VLIW processor, and we assess its impact on the overall performance and area of the processor.

# 5 Soft Processor Datapath Customization Using a Multi-ported Register File

To demonstrate the flexibility of our multi-ported register file and assess its impact on the overall performance and area of a high-performance soft processor core, we used two instances of our register file to customize the datapath of a configurable soft VLIW processor based on [12]. The datapath uses separate register files, DRF and ARF, for storing data and memory addresses, respectively. As the number of functional units in the datapath is increased, more register ports are generally needed to provide access to operands and results. For this experiment, we used our register file architecture to implement the DRF for two configurations of the processor datapath, DP1 and DP2. We configured the DRF of the first processor datapath (DRF1) as a  $32 \times 32$ -bit register file with 8 read ports

| Datapath | IPC | Cloc      | k        | Slices | $\overline{ m BRAMs}$ | MULT18×18 |

|----------|-----|-----------|----------|--------|-----------------------|-----------|

|          |     | Frequency | Period   |        |                       |           |

| DP1      | 5   | 132.4 MHz | 7.55  ns | 2,347  | 23                    | 6         |

| DP2      | 8   | 119.3 MHz | 8.38  ns | 5,152  | 65                    | 12        |

Table 2. Performance and FPGA resource utilization of DP1 and DP2

Table 3. Performance and FPGA resource utilization of DRF1 and DRF2

| Register | Word    | Register | Read  | Write | Latency              | Slices | $\mathbf{BRAMs}$ |

|----------|---------|----------|-------|-------|----------------------|--------|------------------|

| File     | Length  | Size     | Ports | Ports |                      |        |                  |

| DRF1     | 32 bits | 32       | 8     | 2     | 2.94 ns              | 128    | 16               |

| DRF2     | 32 bits | 64       | 14    | 4     | $3.61 \mathrm{\ ns}$ | 465    | 56               |

and 2 write ports. We then configured the DRF of the second processor datapath (DRF2) as a  $64 \times 32$ -bit register file with 14 read and 4 write ports.

Tables 2 and 3 show the performance and resource utilization of the two datapaths and register files, respectively. For each processor, we show the maximum number of instructions executable per clock cycle (IPC), the processor clock frequency and corresponding period, and the number of FPGA slices, BRAMs, and hardware multipliers used to implement the datapath. For each register file we show the corresponding latency and the number of FPGA slices and BRAMs used to implement the register file. Our results show that DRF1 uses 5.5% of the slices and 69.6% of the BRAMs used to implement DP1, and that its latency corresponds to 38.9% of the processor clock period. Our results also show that DRF2 uses 9.0% of the slices and 86.2% of the BRAMs used to implement DP2, and that its latency corresponds to 43.1% of the processor clock period. While the high BRAM utilization is expected – BRAMs are, after all, only used to implement register files and data memories – these results demonstrate the flexibility, performance, and area efficiency of our multi-ported register file.

## 6 Related Work

The use of embedded BRAMs to implement register files is a well known microarchitectural optimization for the efficient implementation of soft processor cores [4]. As soft processor architectures evolve to include wide instruction issue [5,12], multithreading [6], and customized datapaths [7], multi-ported register files become necessary. However, while most of the register files used in these processors provide multiple read ports, none, to the best of our knowledge, provides efficient support for multiple write ports.

Due to their central role in exploiting high levels of instruction parallelism, the design of efficient multi-ported register files for high-performance, general-purpose processors has been the subject of much research [13]. Most techniques focus on partitioning the register file into multiple banks with few ports each to improve access time and reduce area and power consumption. [14,15,16]. We

also partition our register file into multiple banks, and benefit from BRAMs with latencies that are much smaller than the typical clock period of a soft processor. In [17], the register file is partitioned to reduce the number of ports in each partition, and data is duplicated to ensure data consistency. However, an additional clock cycle is needed to update the other partition when one of the partitions is updated. In our implementation we avoid this problem by connecting all BRAMs that contain duplicate information to the same write port, thus ensuring all BRAMs are updated simultaneously.

### 7 Conclusions and Future Work

In this paper we described and evaluated the architecture of a configurable, multi-ported register file for soft processor cores. Our register file is designed around the low-latency embedded memory blocks found in contemporary high-denisty FPGAs such as the Xilinx Virtex-4 FPGA. Our results show that both the latency of the register file and its utilization of FPGA resources are proportional to the product of its word length and the number of its read and write ports. The latency of the register file also depends on the latency of individual BRAM blocks. When integrated into the datapath of a configurable VLIW soft processor, our register file architecture provided the flexibility to support processor datapath customization while exhibiting low latencies and occupying a small proportion of the processor datapath.

To continue this work, we are developing register file latency and area models that we will use in a soft VLIW processor architecture exploration tool. We are also assessing the power consumption characteristics of our register file with the aim of also developing a power model for our register file architecture. Finally, we are developing new register allocation and instruction scheduling passes for our port of the GCC compiler to handle the proposed register file architecture.

#### References

- 1. MicroBlaze Processor Reference Guide. http://www.xilinx.com.

- 2. NIOS-II Processor Reference Handbook. http://www.altera.com.

- 3. P. Yiannacouras, J. G. Steffan, and J. Rose, "Application-Specific Customization of Soft Processor Microarchitecture", *Proceedings of the 14th ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA 2006)*, pp. 201–210, ACM, Feb. 22-24, 2006.

- 4. Xilinx Corportaion, "Using Block RAM in Spartan-3 Generation FPGAs", Xilinx Application Note XAPP463 (v2.0), March 1, 2005.

- A. Jones et al., "An FPGA-based VLIW Processor with Custom Hardware Execution", Proceedings of the 13th ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA 2005), pp. 107-117, ACM, Feb. 20-22, 2005.

- R. Dimond, O. Mencer, and W. Luk, "CUSTARD A Customizable Threaded FPGA Soft Processor and Tools", Proceedings of the International Conference on Field Programmable Logic and Applications (FPL 2005), pp. 1–6, IEEE, Aug. 24-26, 2005.

- D. Jain et al. "Automatically Customizing VLIW Architectures with Coarse-Grained Application-Specific Functional Units", Proceedings of the Eighth International Workshop on Software and Compilers for Embedded Systems (SCOPES 2004), pp. 17-32, Springer Berlin/Heidelberg, Sept. 2-3, 2004.

- 8. Virtex-4 User Guide, UG070 (v1.6), http://www.xilinx.com, Oct. 6, 2006.

- 9. Steven Muchnick, Advanced Compiler Design and Implementation, Morgan Kaufmann Publishers/Elsevier, 1997.

- John L. Hennessy and David A. Patterson, Computer Architecture: A Quantitative Approach, Third Edition, Morgan Kaufmann Publishers/Elsevier, 2003.

- 11. Development System Reference Guide (8.2i), http://www.xilinx.com.

- M. A. R. Saghir, M. El-Majzoub, and P. Akl, "Customizing the Datapath and ISA of Soft VLIW Processors", Proceedings of the 2007 International Conference on High Performance Embedded Architectures and Compilers (HiPEAC 2007), pp. 276–290, Springer LNCS 4367, Jan. 28-30, 2007.

- K. Farkas, N. Jouppi, and P. Chow, "Register File Design Considerations in Dynamically Scheduled Processors", Proceedings of the 2nd IEEE Symposium on High-Performance Computer Architecture, pp. 40–51, IEEE, 1996.

- J. L. Cruz et al., "Multiple-Banked Register File Architectures", Proceedings of the 27th Annual International Symposium on Computer Architecture (ISCA 2000), pp. 316–325, ACM, 2000.

- J. Zalema et al., "Two-Level Hierarchical Register File Organization for VLIW Processors", Proceedings of the 33rd Annual ACM/IEEE International Symposium on Microarchitecture (MICRO 2000), pp. 137–146, ACM/IEEE, 2000.

- J. H. Tseng and K. Asanovic, "Banked Multiported Register Files for High-Frequency Superscalar Microprocessors", Proceedings of the 30th Annual International Symposium on Computer Architecture (ISCA 2003), pp. 62–71, ACM, 2003.

- 17. R. E. Kessler, E. J. McLellan, and D. A. Webb, "The Alpha 21264 Microprocessor Architecture", *Proceedings of the International Conference on Computer Design* (ICCD'98), pp. 90–95, IEEE, 1998.

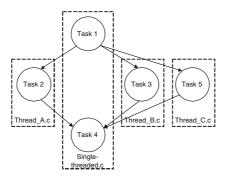

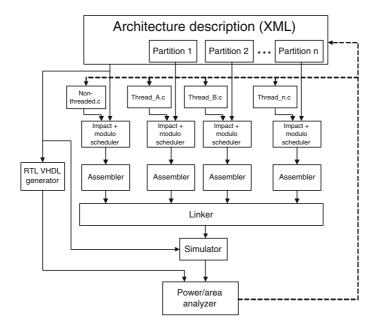

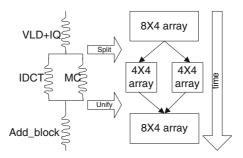

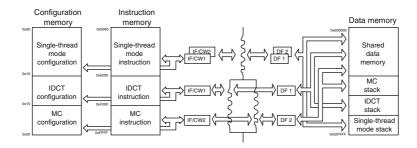

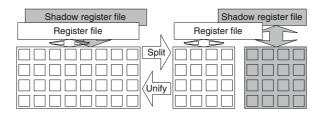

# MT-ADRES: Multithreading on Coarse-Grained Reconfigurable Architecture

Kehuai Wu<sup>1</sup>, Andreas Kanstein<sup>2</sup>, Jan Madsen<sup>1</sup>, and Mladen Berekovic<sup>3</sup>